Base addresses, Base addresses –3 – Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 62

Chapter 6: 10M-10GbE MAC with IEEE 1588v2 Design Example

6–3

10M-10GbE MAC with IEEE 1588v2 Design Example Files

February 2014

Altera Corporation

10-Gbps Ethernet MAC MegaCore Function User Guide

■

Ethernet ToD Clock—provides 64-bits and/or 96-bits time-of-day to TX and RX of

10GbE Ethernet MAC.

■

Pulse Per Second Module—returns pulse per second (pps) to user.

■

Avalon-MM Master Translator—provides access to the registers of the following

components through the Avalon-MM interface:

■

MAC

■

Backplane Ethernet 10GBASE-KR PHY

■

Transceiver Reconfiguration Controller

■

ToD Clock

6.2.1. Base Addresses

lists the design example components that you can reconfigure to suit your

verification objectives. To reconfigure the components, write to their registers using

the base addresses listed in the table and the register offsets described in the

components' user guides.

1

This design example uses a 19-bit width address bus to access the base address of

components other than the MAC.

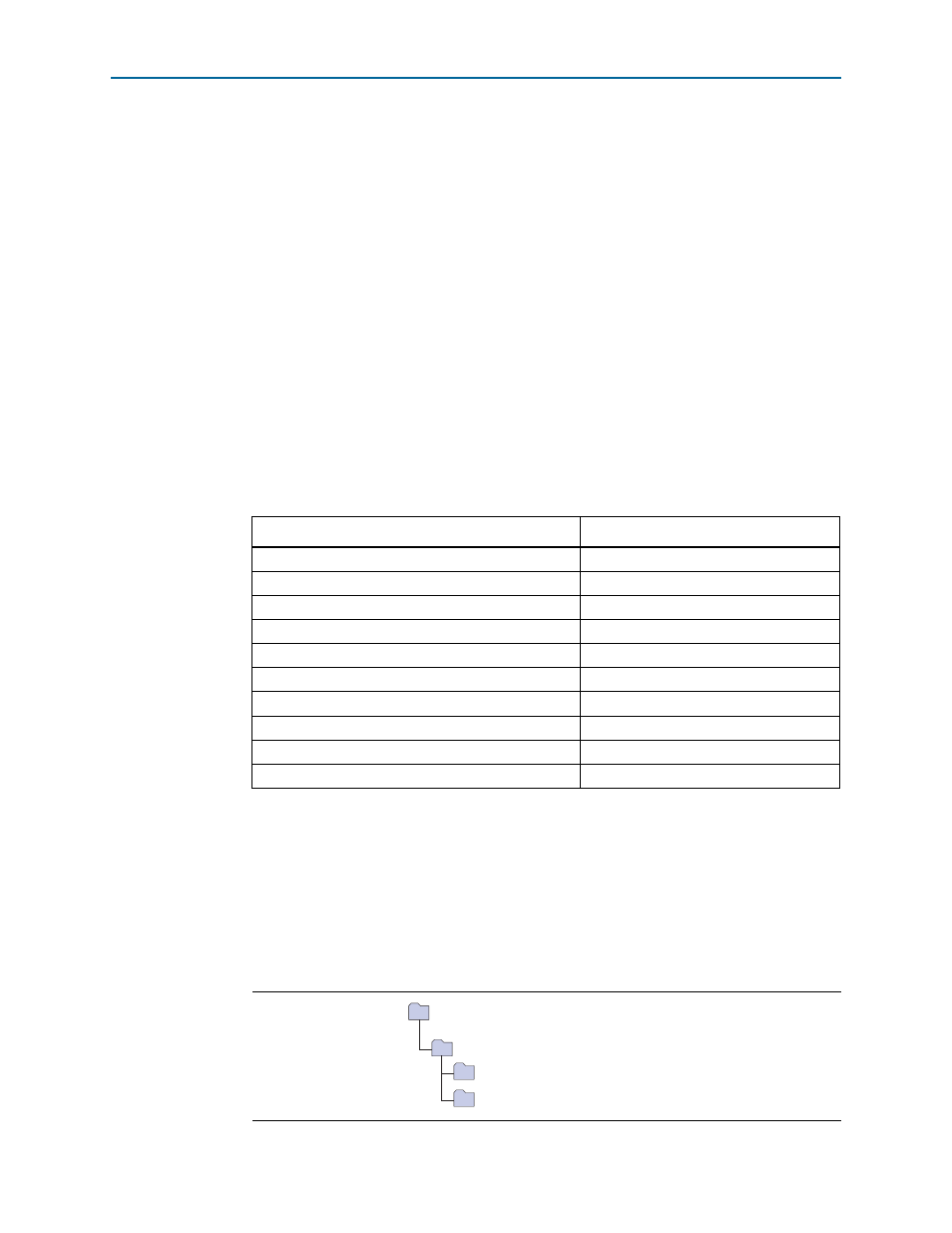

6.3. 10M-10GbE MAC with IEEE 1588v2 Design Example Files

shows the directory structure for the 10M-10GbE MAC with IEEE 1588v2

design examples and testbenches.

Table 6–1. Base Addresses of 10M-10GbE MAC with IEEE 1588v2 Design Example Components

Component

Base Address

MAC Channel 0

0x00000

MAC Channel 1

0x20000

Backplane Ethernet 10GBASE-KR PHY Channel 0

0x80000

Backplane Ethernet 10GBASE-KR PHY Channel 1

0x80800

Configure Reconfiguration Channel 0

0x80400

Configure Reconfiguration Channel 1

0x80500

Time of Day Clock (1G) Channel 0

0x81100

Time of Day Clock (10G) Channel 0

0x81000

Time of Day Clock (1G) Channel 1

0x81300

Time of Day Clock (10G) Channel 1

0x81200

Figure 6–2. 10M-10GbE MAC with IEEE 1588v2 Design Example Folders

altera_eth_10g_mac_base_kr_1588

testbench

reconfig