Timing diagrams—ieee 1588v2 timestamp, Timing diagrams—ieee 1588v2 timestamp –27 – Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 146

Chapter 9: Interface Signals

9–27

February 2014

Altera Corporation

10-Gbps Ethernet MAC MegaCore Function User Guide

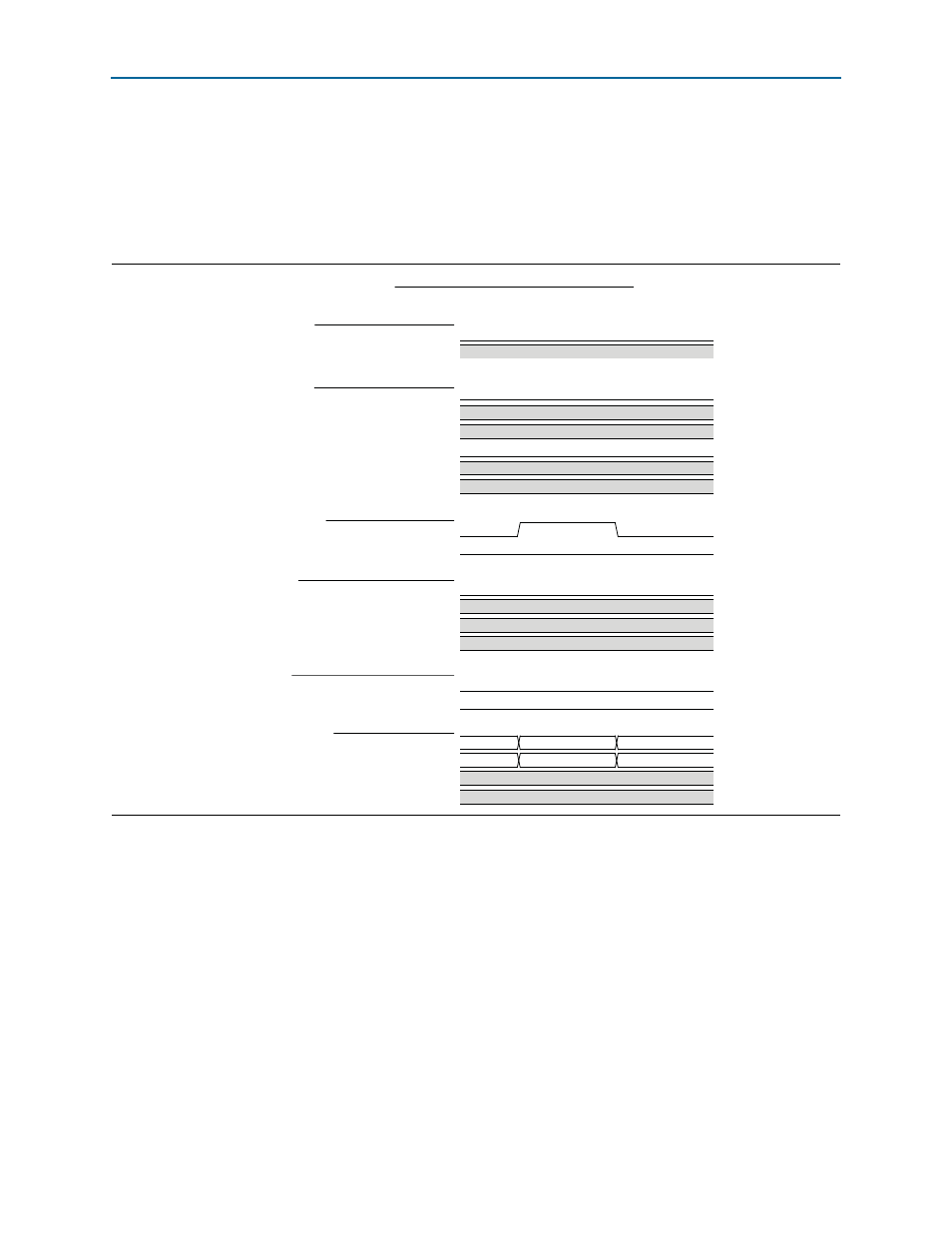

9.0.9.4. Timing Diagrams—IEEE 1588v2 Timestamp

The following timing diagrams show the timestamp of frames observed on the TX

path for the IEEE 1588v2 feature.

shows the TX timestamp signals for the IEEE 1588v2 feature in a one step

operation.

Figure 9–9. Egress Timestamp Insert for IEEE 1588v2 PTP Packet Encapsulated in IEEE 802.3

Egress Timestamp Insert, IEEE 1588v2, PTP Packet

2-step Timestamp Request,Input

tx_egress_timestamp_request_valid

tx_egress_timestamp_request_data[N:0]

2-step Timestamp Return,Output

tx_egress_timestamp_96b_valid

tx_egress_timestamp_96b_fingerprint[N:0]

tx_egress_timestamp_96b_data[95:0]

tx_egress_timestamp_64b_valid

tx_egress_timestamp_64b_fingerprint[N:0]

tx_egress_timestamp_64b_data[63:0]

1-step Timestamp Insert,Input

tx_etstamp_ins_ctrl_timestamp_insert

tx_etstamp_ins_ctrl_timestamp_format

1-step Residence Time Update,Input

tx_etstamp_ins_ctrl_residence_time_update

tx_etstamp_ins_ctrl_ingress_timestamp_96b[95:0]

tx_etstamp_ins_ctrl_ingress_timestamp_64b[63:0]

tx_etstamp_ins_ctrl_residence_time_calc_format

1-step IPv4 and IPv6 Checksum,Input

tx_etstamp_ins_ctrl_checksum_zero

tx_etstamp_ins_ctrl_checksum_correct

1-step Location Offset,Input

tx_etstamp_ins_ctrl_offset_timestamp[15:0]

Offset 1

Don’t-care

Don’t-care

Don’t-care

Don’t-care

Don’t-care

Don’t-care

Don’t-care

Don’t-care

Don’t-care

Don’t-care

tx_etstamp_ins_ctrl_offset_correction_field[15:0]

Offset 2

tx_etstamp_ins_ctrl_offset_checksum_field[15:0]

tx_etstamp_ins_ctrl_offset_checksum_correction[15:0]