B.6.1. adjusting tod’s drift – Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 161

Appendix B: Time-of-Day (ToD) Clock

B–5

February 2014

Altera Corporation

10-Gbps Ethernet MAC MegaCore Function User Guide

B.6.1. Adjusting ToD’s Drift

You can use the DriftAdjust and DriftAdjustRate registers to correct any drift in the

ToD clock.

For example, in the case of a ToD for 10G with period of 6.4ns, the nanosecond field is

converted directly to PERIOD_NS while the fractional nanosecond need to be

multiplied with 2

16

or 65536 in order to convert to PERIOD_FNS. This results in 0x6

PERIOD_NS

and 0x6666.4 PERIOD_FNS.

PERIOD_NS

only accepts 0x6666 and ignores 0x0000.4, which in turn would cause some

inaccuracy in the configured period. This inaccuracy will cause the ToD to drift from

the actual time as much as 953.67ns after a period of 1 second. You would notice that

after every 5 cycles, 0x0000.4 accumulates to 0x0002. If the TOD is able to add 0x0002

of fractional nanosecond into the ToD once after every period of 5 cycles, then it will

correct the drift.

Therefore, for the 10G case, DRIFT_ADJUST_NS is now configured to 0x0,

DRIFT_ADJUST_FNS

is configured to 0x0002 and ADJUST_RATE is configured to 0x5.

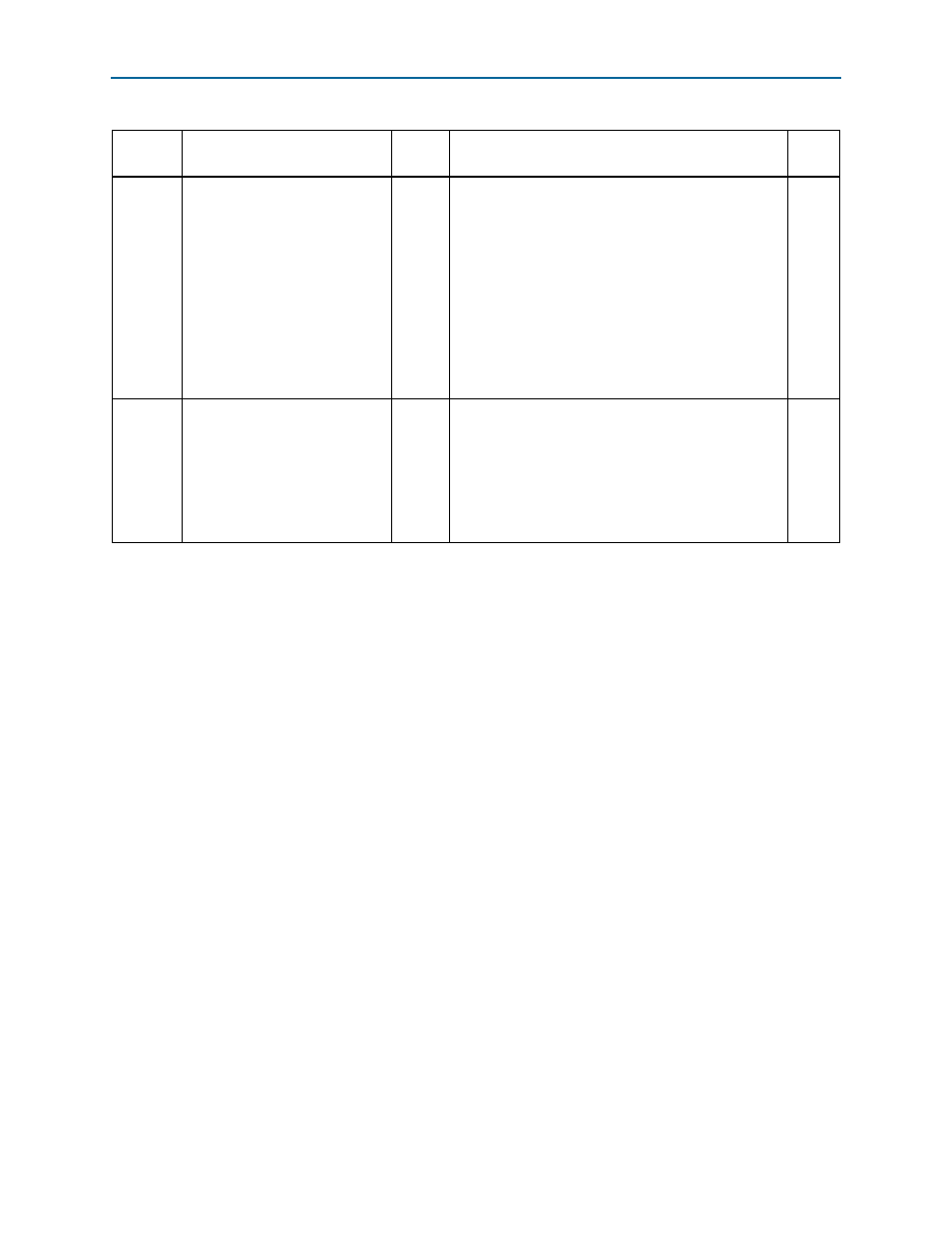

0x1C

DriftAdjust

RW

The drift of ToD adjusted periodically by adding a

correction value as configured in this register space.

■

Bits 0 to 15: Adjustment value in fractional

nanosecond (DRIFT_ADJUST_FNS). This value is

added into the current ToD during the adjustment.

The default value is 0.

■

Bits 16 to 19: Adjustment value in nanosecond

(DRIFT_ADJUST_NS). This value is added into the

current ToD during the adjustment. The default value

is 0.

■

Bits 20 to 32: Not used.

0x0

0x20

DriftAdjustRate

RW

The count of clock cycles for each ToD’s drift adjustment

to take effect.

■

Bits 0 to 15: The number of clock cycles

(ADJUST_RATE). The ToD adjustment happens once

after every period in number of clock cycles as

indicated by this register space.

■

Bits 16 to 32: Not used.

0x0

Table B–6. ToD Clock Registers (Part 2 of 2)

Byte

Offset

Name

R/W

Description

HW

Reset