10gbe mac and phy connection with xgmii – Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 151

10–2

Chapter 10: Design Considerations

10GbE MAC and PHY Connection with XGMII

10-Gbps Ethernet MAC MegaCore Function User Guide

February 2014

Altera Corporation

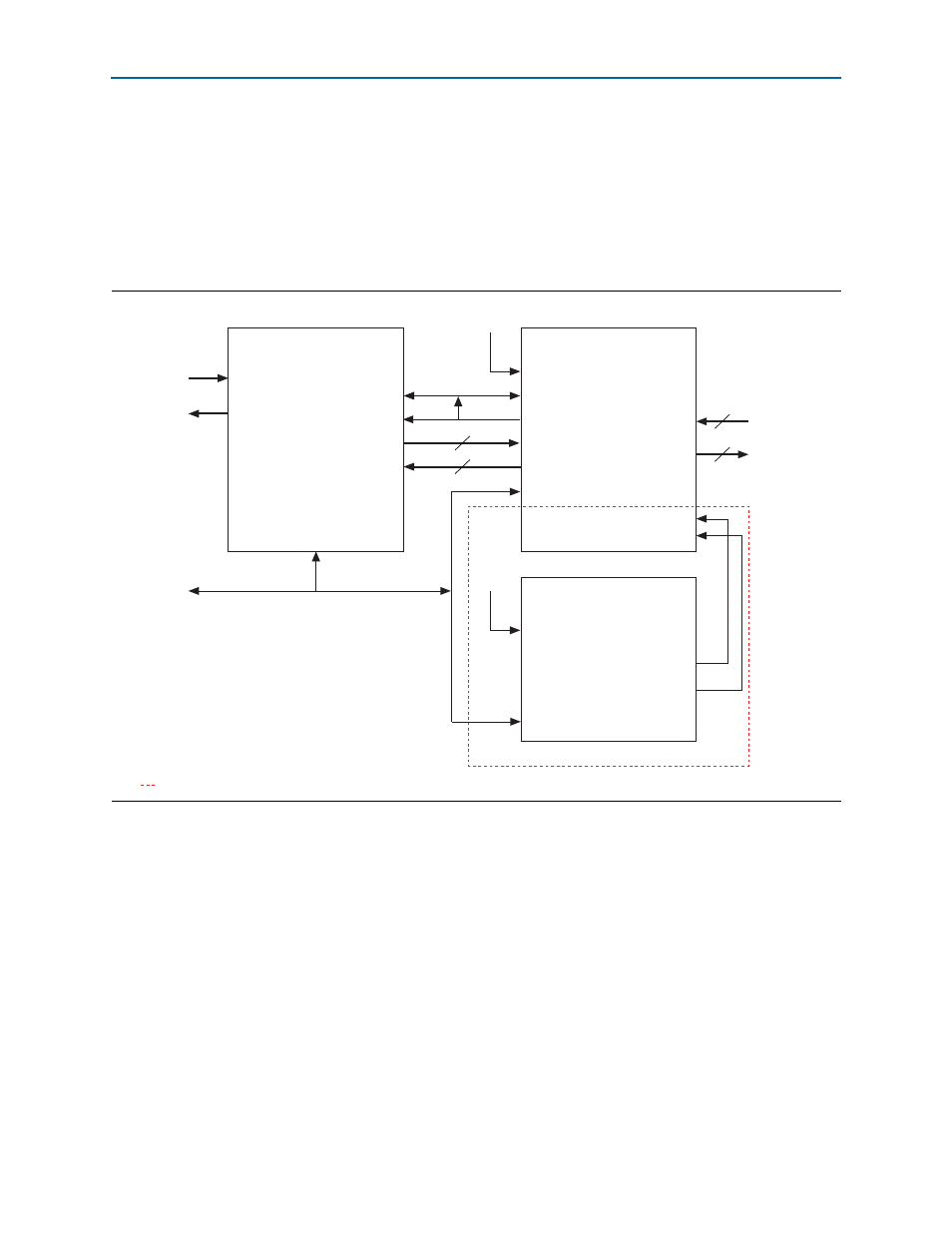

10.2. 10GbE MAC and PHY Connection with XGMII

The XGMII is defined by the IEEE802.3 standard. XGMII is the standard interface

between the MAC and PHY in the 10G Ethernet solution. Altera 10G MAC and PHY

connect easily using the SDR XGMII interface.

shows an example of an SDR XGMII connection between the 10G MAC

and PHY IP.

10.3. Sharing TX and RX Clocks for Multi-Port System Design

In a multi-port system design, you may need to share the MAC TX and RX clock for

1G and 10G with all ports. In such cases, your design requires only one ToD for each

clock domains. The ToD Sync module will synchronize between the 1G and 10G MAC

depending on which you select as the master ToD.

If the ports do not share the clocks, each clock domain in every port will require a

dedicated ToD that is synchronized to the master ToD.

Figure 10–1. 10G MAC and PHY Connection with XGMII Interface

10GbE MAC

XAUI/10G BASE-R PHY

Reconfiguration Controller

Avalon ST TX

Avalon ST RX

tx_clk_clk

rx_clk_clk

xgmii_rx_data

xgmii_tx_data

xgmii_tx_clk

xaui_rx_serial_

data[3:0]/rx_serial_data

xaui_tx_serial_

data[3:0]/tx_serial_data

xgmii_rx_clk

pll_ref_clk

xgmii_rx_dc

phy_mgmt interface

xgmii_tx_dc

reconfig_from_xcvr

reconfig_to_xcvr

mgmt_clk_clk

reconfig_mgmt interface

reconfig_from_xcvr

reconfig_to_xcvr

csr interface

72

72

4/1

4/1

SDR XGMII

[email protected] Mhz/

10G [email protected] Mhz

[email protected] Gbps/

10G [email protected] Gbps

Avalon MM

Your design does not require the reconfiguration controller if you use Arria II GX/GT, Cyclone IV GX, or Stratix IV GX/GT devices.

Avalon MM

Clock