Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 63

6–4

Chapter 6: 10M-10GbE MAC with IEEE 1588v2 Design Example

Creating a New 10M-10GbE MAC with IEEE 1588v2 Design

10-Gbps Ethernet MAC MegaCore Function User Guide

February 2014

Altera Corporation

lists the files in the ..\altera_eth_10g_mac_base_kr_1588 directory.

6.4. Creating a New 10M-10GbE MAC with IEEE 1588v2 Design

You can use the Quartus II software to create a new 10M-10GbE MAC with IEEE

1588v2 design. Altera provides a Qsys design example file that you can customize to

facilitate the development of your 10M-10GbE MAC with IEEE 1588v2 design.

To create the design, perform the following steps:

1. Launch the Quartus II software and open a new Quartus II Project.

2. Run add_design_example_files.tcl in the Quartus II software to add the required

design example files to the project.

3. Launch Qsys from the Tools menu and open the

altera_eth_10g_mac_base_kr_1588.qsys

file.

4. Turn off the additional module under the Use column if your design does not

require it. This action disconnects the module from the 10M-10GbE MAC with

IEEE 1588v2 system.

5. Double-click on eth_10g_design_example_0 and eth_10g_design_example_1 to

launch the parameter editor.

6. Specify the required parameters in the parameter editor.

7. Click Finish.

8. On the Generation tab, select either a Verilog HDL or VHDL simulation model

and make sure that the Create HDL design files for synthesis option is turned on.

9. Click Generate to generate the simulation and synthesis files.

10. Launch the MegaWizard Plug-in Manager from the Tools menu. Select Edit an

existing custom megafunction variation

and regenerate reconfig.v from the

reconfig

folder.

11. Click Finish.

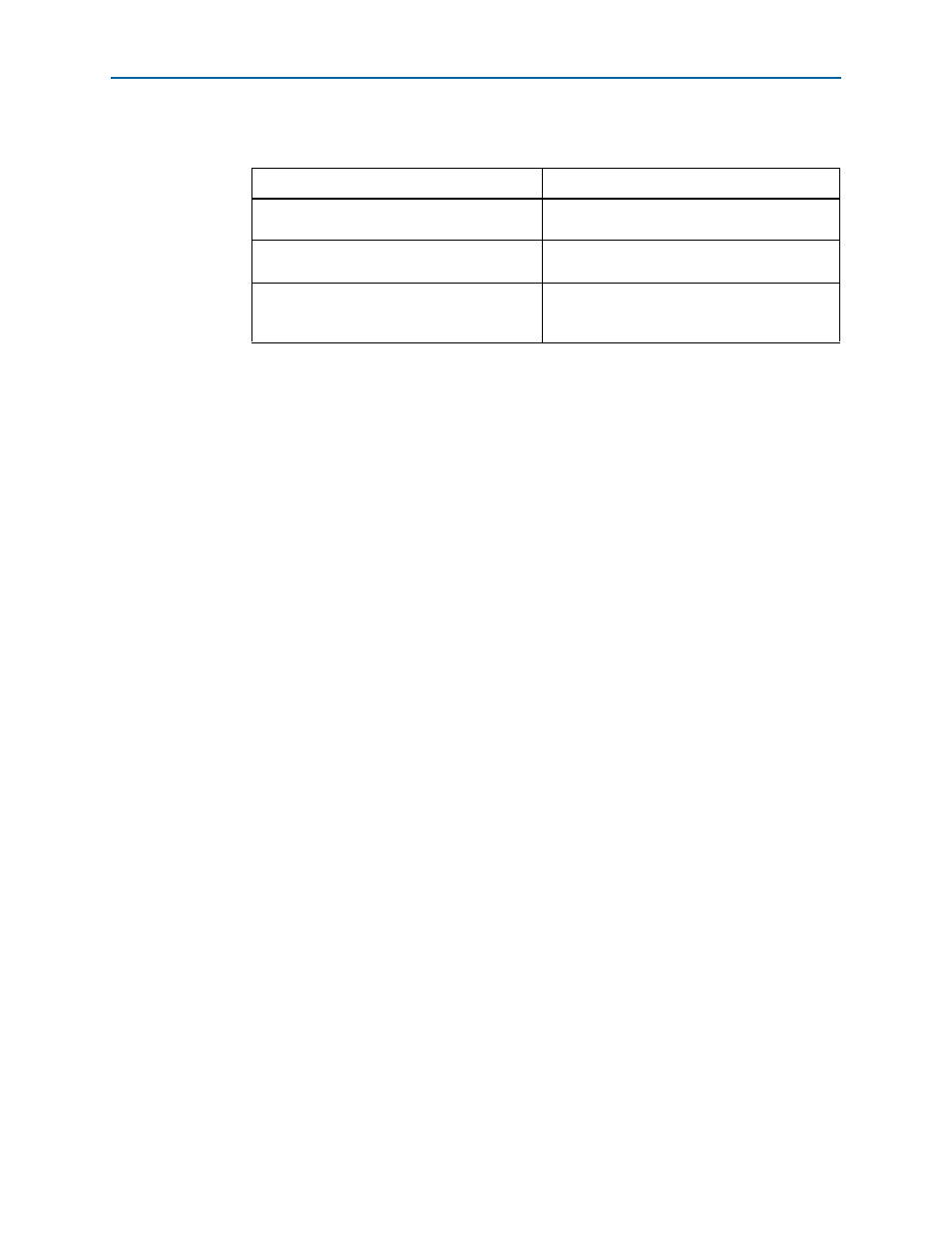

Table 6–2. 10M-10GbE MAC with IEEE 1588v2 Design Example Files

File Name

Description

altera_eth_10g_mac_base_kr_1588_top.sv

The top-level entity file of the design example for

verification in hardware.

altera_eth_10g_mac_base_kr_1588_top.sdc

The Quartus II SDC constraint file for use with

the TimeQuest timing analyzer.

altera_eth_10g_mac_base_kr_1588.qsys

A Qsys file for the 10M-10GbE MAC and

10GBASE-KR PHY design example with IEEE

1588v2 option enabled.