1g/10gbe simulation timing diagrams, 1g/10gbe simulation timing diagrams –12 – Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 57

5–12

Chapter 5: 1G/10GbE MAC Design Example

1G/10GbE Testbench

10-Gbps Ethernet MAC MegaCore Function User Guide

February 2014

Altera Corporation

# broadcastFramesErr = 0

# etherStatsOctets = 5310

# etherStatsPkts = 8

# etherStatsUndersizePkts = 0

# etherStatsOversizePkts = 0

# etherStatsPkts64Octets = 4

# etherStatsPkts65to127Octets = 0

# etherStatsPkts128to255Octets = 0

# etherStatsPkts256to511Octet = 1

# etherStatsPkts512to1023Octets = 0

# etherStatsPkts1024to1518Octets = 3

# etherStatsPkts1519OtoXOctets = 0

# etherStatsFragments = 0

# etherStatsJabbers = 0

# etherStatsCRCErr = 0

# unicastMACCtrlFrames = 0

# multicastMACCtrlFrames = 0

# broadcastMACCtrlFrames = 0

1

The same message will appear twice if you use 1G/10G Ethernet mode

because the system resets the statistic counters after changing the MAC

operating speed.

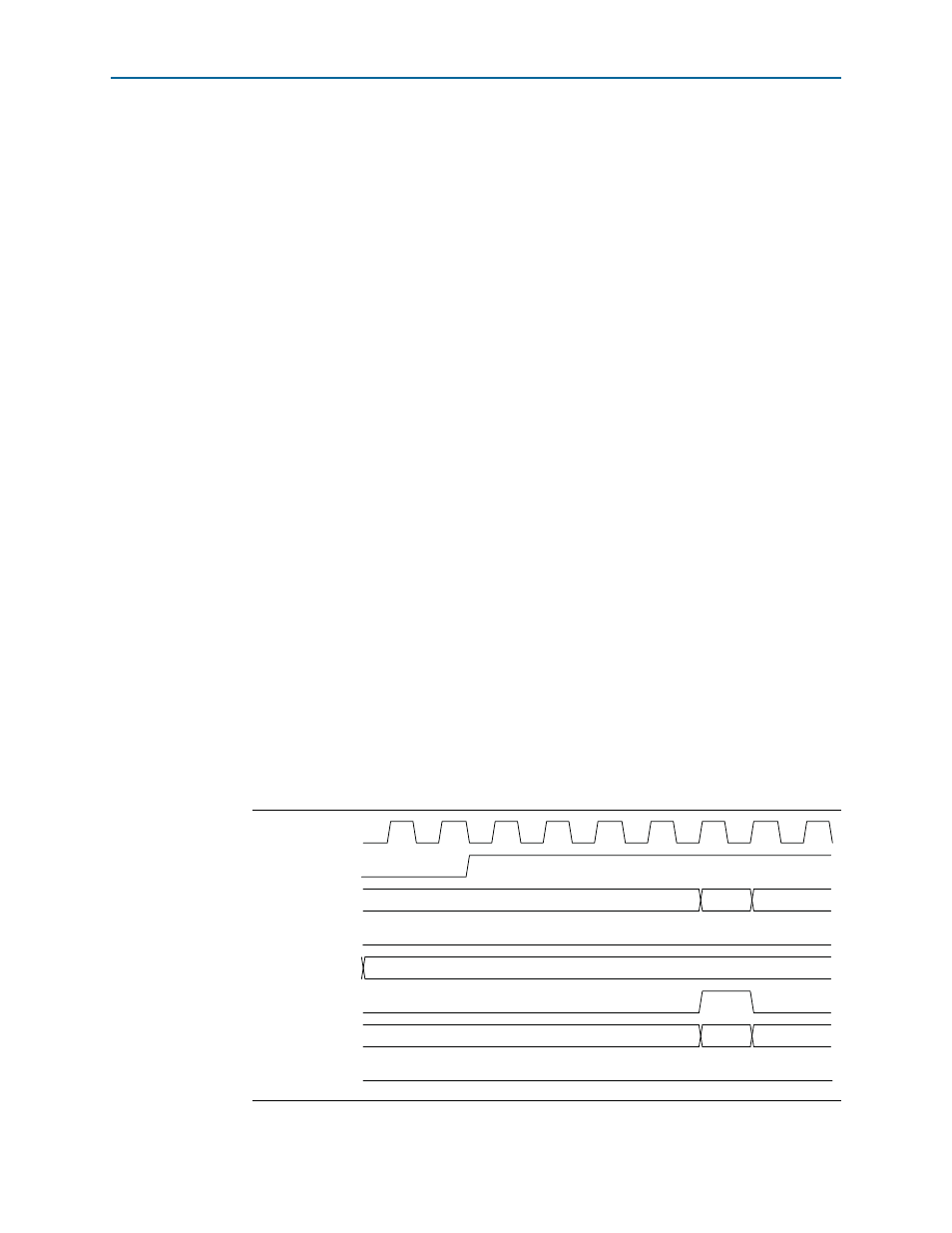

5.5.6. 1G/10GbE Simulation Timing Diagrams

shows the reset and initial configuration sequence. The first read or write

transaction must be at least one clock cycle after the csr_reset_reset_n signal

completes.

Figure 5–5. Reset and Configuration

csr_clk_clk

csr_reset_reset_n

csr_address [18:0]

csr_read

csr_readdata [31:0]

csr_write

csr_writedata [31:0]

csr_waitrequest

40084

00000002