10gbe with ieee 1588v2 testbench files, 10gbe with ieee 1588v2 testbench files –6 – Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 44

4–6

Chapter 4: 10GbE MAC with IEEE1588v2 Design Example

10GbE with IEEE 1588v2 Testbench

10-Gbps Ethernet MAC MegaCore Function User Guide

February 2014

Altera Corporation

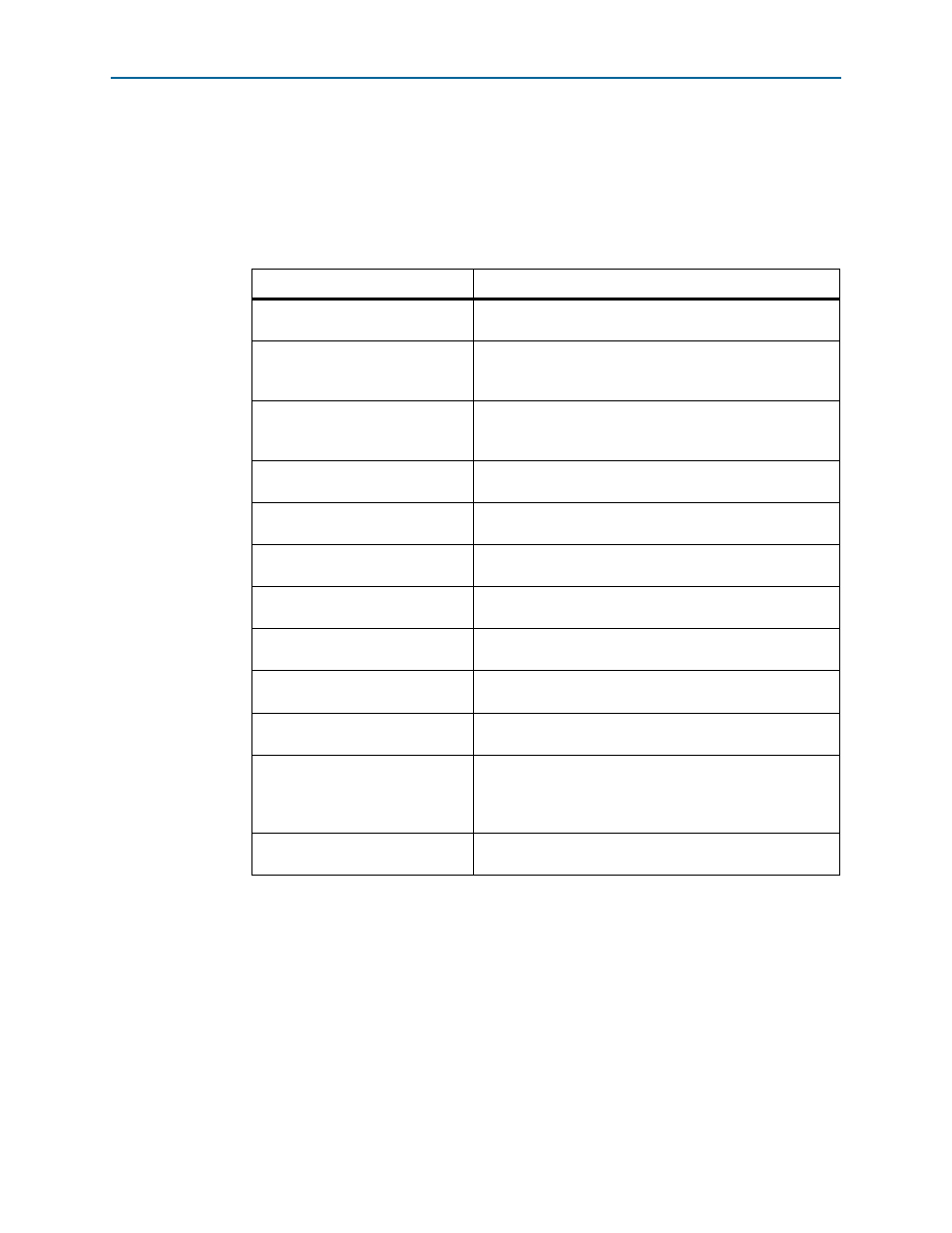

4.5.3. 10GbE with IEEE 1588v2 Testbench Files

The <ip

library>/ethernet/altera_eth_10g_design_example/altera_eth_10g_mac_base_r_1588

/testbench

directory contains the testbench files.

Table 4–3

describes the files that implement the 10GbE with IEEE 1588v2 testbench.

Table 4–3. 10GbE with IEEE 1588v2 Testbench Files

File Name

Description

avalon_bfm_wrapper.sv

A wrapper for the Avalon BFMs that the avalon_driver.sv file

uses.

avalon_driver.sv

A SystemVerilog HDL driver that utilizes the BFMs to exercise

the transmit and receive path, and access the Avalon-MM

interface.

avalon_if_params_pkg.sv

A SystemVerilog HDL testbench that contains parameters to

configure the BFMs. Because the configuration is specific to

the DUT, you must not change the contents of this file.

avalon_st_eth_packet_monitor.sv

A SystemVerilog HDL testbench that monitors the Avalon-ST

transmit and receive interfaces.

default_test_params_pkg.sv

A SystemVerilog HDL package that contains the default

parameter settings of the testbench.

eth_mac_frame.sv

A SystemVerilog HDL class that defines the Ethernet frames.

The avalon_driver.sv file uses this class.

eth_register_map_params_pkg.sv

A SystemVerilog HDL package that maps addresses to the

Avalon-MM control registers.

ptp_timestamp.sv

A SystemVerilog HDL class that defines the timestamp in the

testbench.

tb_run_simulation.tcl

A Tcl script that starts a simulation session in the ModelSim

simulation software.

tb_testcase.sv

A SystemVerilog HDL testbench file that controls the flow of

the testbench.

tb_top.sv

The top-level testbench file. This file includes the customized

10GbE MAC, which is the device under test (DUT), a client

packet generator, and a client packet monitor along with

other logic blocks.

wave.do

A signal tracing macro script for use with the ModelSim

simulation software to display testbench signals.