Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 107

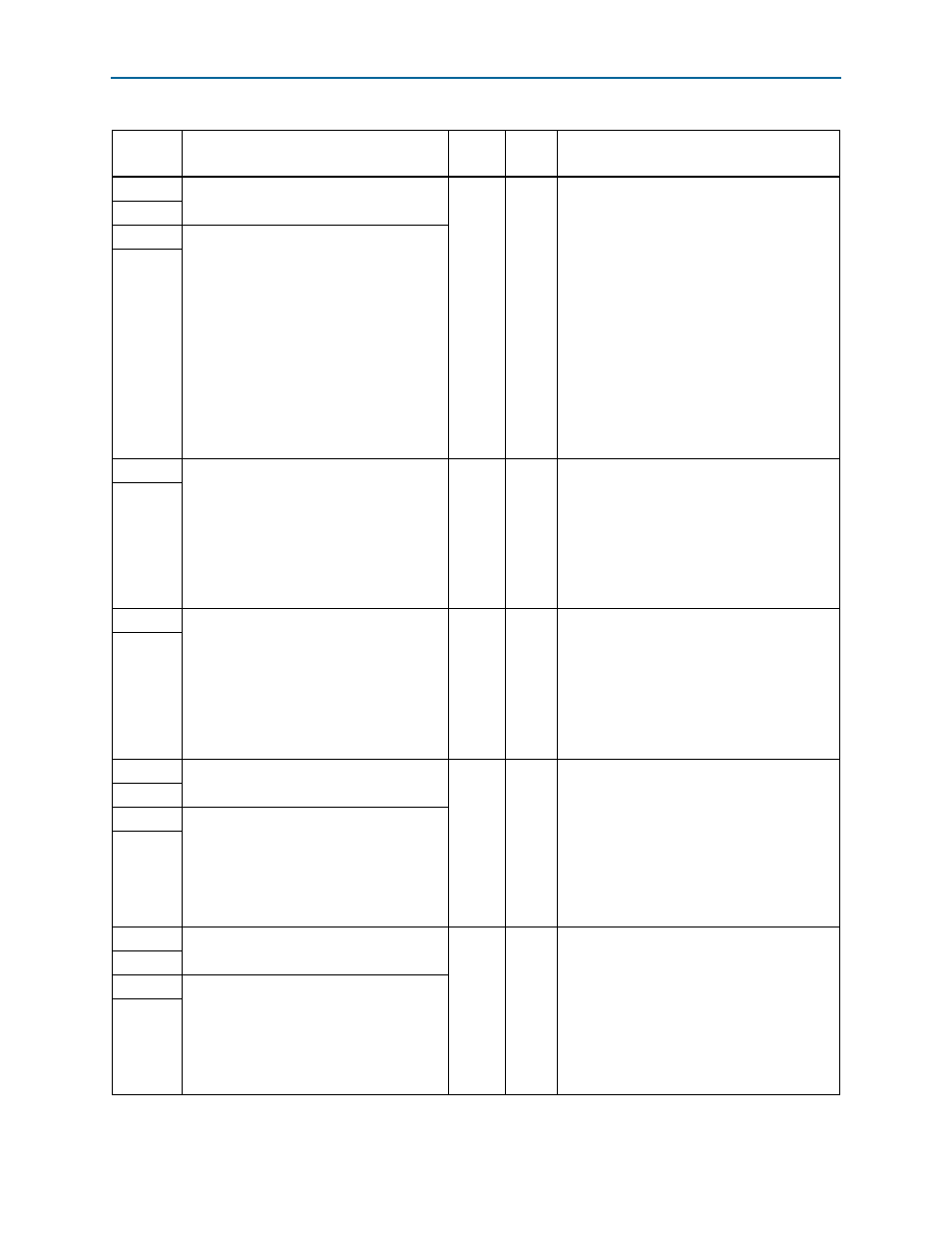

Chapter 8: Registers

8–13

MAC Registers

February 2014

Altera Corporation

10-Gbps Ethernet MAC MegaCore Function User Guide

0x0C1E

rx_stats_etherStats UndersizePkts

RO

0x0

■

Bit 0—The number of undersized frames

(frame length less than 64 bytes, including

the CRC field) received or transmitted.

■

36-bit width register:

■

0x0C1E and 0x0C1F = bits [31:0]

■

0x1C1E and 0x1C1F = bits [35:32]

■

If you set the statistics counters to

memory-based implementation, it takes a

longer processing time to update the

registers. The number of undersized frames

received or transmitted may not increment

if they need to be updated multiple times in

a short period.

0x0C1F

0x1C1E

tx_stats_etherStats UndersizePkts

0x1C1F

0x0C20

rx_stats_etherStats OversizePkts

RO

0x0

■

Bit 0—The number of oversized frames

(frame length more than

rx_frame_maxlength

, including the CRC

field) received.

■

36-bit width register:

■

0x0C20 = bits [31:0]

■

0x0C21 = bits [35:32]

0x0C21

0x1C20

tx_stats_etherStats OversizePkts

RO

0x0

■

Bit 0—The number of oversized frames

(frame length more than

tx_frame_maxlength

, including the CRC

field) transmitted.

■

36-bit width register:

■

0x1C20 = bits [31:0]

■

0x1C21= bits [35:32]

0x1C21

0x0C22

rx_stats_etherStats Pkts64Octets

RO

0x0

■

Bit 0—The number of 64-byte receive or

transmit frames, including the CRC field but

excluding the preamble and SFD bytes. This

count includes good, errored, and invalid

frames.

■

36-bit width register:

■

0x0C22 and 0x0C23 = bits [31:0]

■

0x1C22 and 0x1C23 = bits [35:32]

0x0C23

0x1C22

tx_stats_etherStats Pkts64Octets

0x1C23

0x0C24

rx_stats_etherStats

Pkts65to127Octets

RO

0x0

■

Bit 0—The number of receive or transmit

frames between the length of 65 and 127

bytes, including the CRC field but excluding

the preamble and SFD bytes. This count

includes good, errored, and invalid frames.

■

36-bit width register:

■

0x0C24 and 0x0C25 = bits [31:0]

■

0x1C24 and 0x1C25 = bits [35:32]

0x0C25

0x1C24

tx_stats_etherStats

Pkts65to127Octets

0x1C25

Table 8–2. MAC Registers (Part 12 of 15)

Word

Offset

Register Name

Access

Reset

Value

Description