Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 133

9–14

Chapter 9: Interface Signals

10-Gbps Ethernet MAC MegaCore Function User Guide

February 2014

Altera Corporation

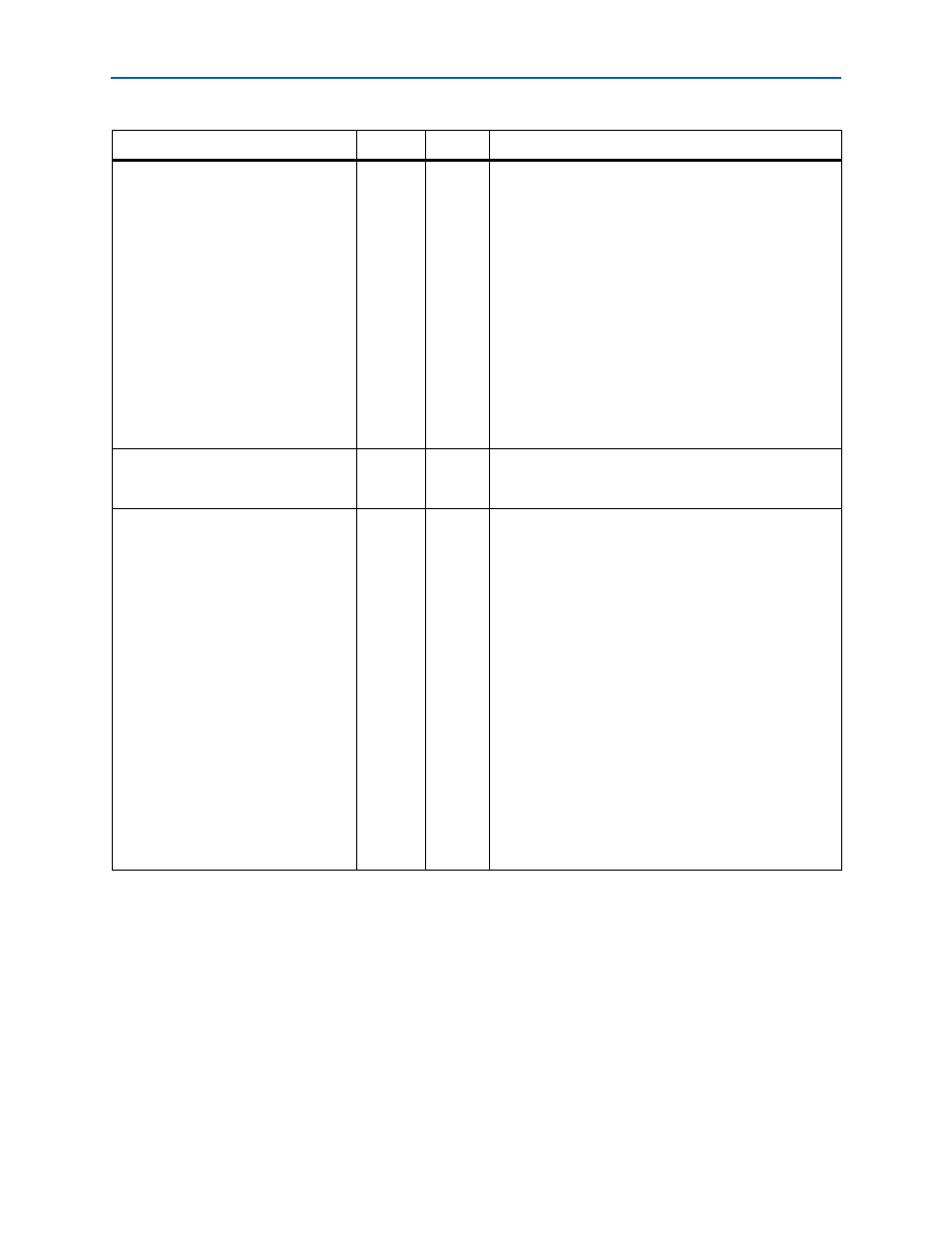

avalon_st_rxstatus_error[]

Output

7

When set to 1, each bit of this signal indicates an error

type in the receive frame.

■

Bit 0: Undersized frame.

■

Bit 1: Oversized frame.

■

Bit 2: Payload length error.

■

Bit 3: CRC error.

■

Bit 4: Unused.

■

Bit 5: Unused.

■

Bit 6: PHY error.

The IP core presents the error status on this bus in the

same clock cycle it asserts

avalon_st_rxstatus_valid

. The error status is invalid

when an overflow occurs.

avalon_st_txstatus_valid

Output

1

When asserted, this signal indicates that

avalon_st_txstatus_data[]

contains valid

information about the transmit frame.

avalon_st_txstatus_data[]

Output

40

Contains information about the transmit frame:

■

Bits 0 to 15: Payload length.

■

Bits 16 to 31: Packet length.

■

Bit 32: When set to 1, indicates a stacked VLAN frame.

■

Bit 33: When set to 1, indicates a VLAN frame.

■

Bit 34: When set to 1, indicates a control frame.

■

Bit 35: When set to 1, indicates a pause frame.

■

Bit 36: When set to 1, indicates a broadcast frame.

■

Bit 37: When set to 1, indicates a multicast frame.

■

Bit 38: When set to 1, indicates a unicast frame.

■

Bit 39: When set to 1, indicates a PFC frame.

The IP core asserts the valid information on this bus in the

same clock cycle it asserts

avalon_st_txstatus_valid

. The information on this

data bus is invalid when an underflow occurs or when CRC

and/or padding insertion is enabled.

Table 9–8. Avalon-ST Status Interface Signals (Part 2 of 5)

Signal

Direction

Width

Description