B. time-of-day (tod) clock, B.1. features, B.2. device family support – Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 157: B.3. performance and resource utilization, Appendix b. time-of-day (tod) clock, Appendix b, time-of-day (tod), Clock

February 2014

Altera Corporation

10-Gbps Ethernet MAC MegaCore Function User Guide

B. Time-of-Day (ToD) Clock

The ToD clock provides a stream of timestamps for the IEEE 1588v2 feature.

B.1. Features

■

Provides a stream of 96-bit timestamps. The timestamp has 48-bit second field,

32-bit nanosecond field, and 16-bit fractional nanosecond field.

■

Runs at 156.25 MHz for the 10GbE MAC IP core.

■

Supports coarse adjustment and fine adjustments through clean frequency

adjustment.

■

Supports period adjustment for frequency control using the

Period

register.

■

Supports offset adjustment using the

AdjustPeriod

register.

■

Automatically synchronizes to the master ToD clock through the ToD

synchronization module when connected.

■

Allows periodic correction if the ToD clock drifts from the actual time.

B.2. Device Family Support

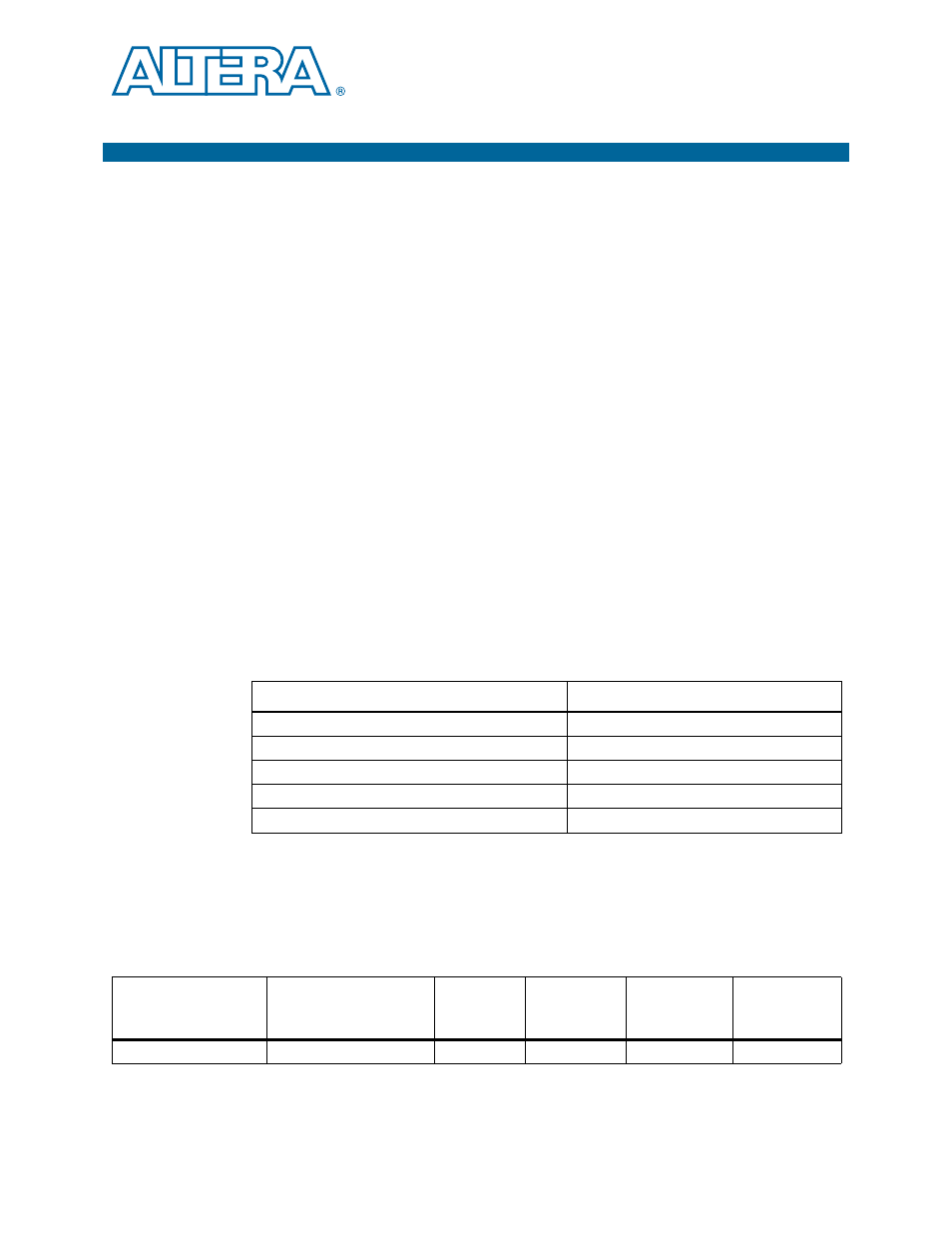

Table B–1

shows the level of support offered by the ToD clock for each Altera device

family.

B.3. Performance and Resource Utilization

Table B–2

provides the estimated resource utilization and performance of the ToD

clock for the Stratix V device family.

Table B–1. Device Family Support

Device Family

Support

Arria V GX/GT/GZ/SOC

Preliminary

Cyclone V

Preliminary

Stratix IV GX/GT

Preliminary

Stratix V GX/GT

Preliminary

Other device families

No support

Table B–2. Stratix V Performance and Resource Utilization

MegaCore Function

Settings

FIFO Buffer

Size

(Bits)

Combinational

ALUTs

Logic Registers

Memory

(M20K Blocks/

MLAB Bits)

ToD Clock

Default

0

378

1,120

0/0