5 vga reference design, Figure 4-42: vga reference design, Page 81 ice module – IEI Integration ICE-DB-9S User Manual

Page 94

Page 81

ICE Module

ICE Module implement the LVDS EDID ROM on board. If Customer want to fix

the resolution or EDID information, please contact IEI for ODM Service.

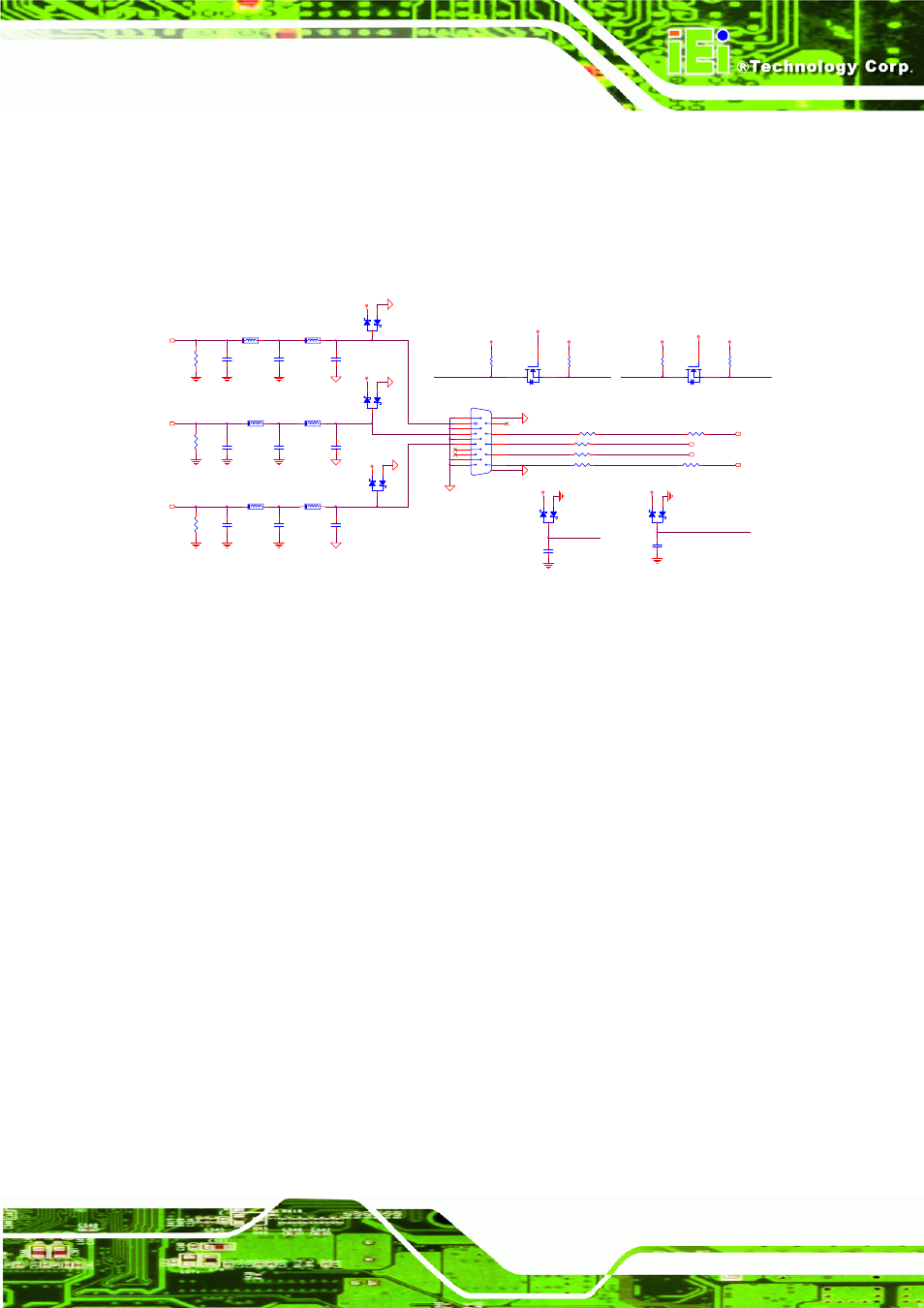

4.13.5 VGA Reference Design

This reference design shows a circuitry implementing a VGA port.

R161

0_4

1

2

R160

33_4

1

2

VGA_HSYNC

VGA_VSYNC

VGA_BLU

VGA_GRN

VGA_RED

+V5

+V3.3

VGA_I2C_CK

R156

@2.2K_4

1

2

R158

@2.7K_4

1

2

Q6

@2N7002_SOT23

D

G

S

+V3.3

VGA_I2C_DAT_Z

C127

@22P_4_N_50V

CRT_R

CRT_B

C126

@22P_4_N_50V

IO_GND

VGA_I2C_CK_Z

IO_GND

VGA_I2C_CK_Z

R162

33_4

1

2

IO_GND

R164

33_4

1

2

IO_GND

R165

33_4

1

2

IO_GND

VGA

IO_GND

CRT_R_Y

IO_GND

CON7

VGA SOCKET

<1ST PART FIELD>

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

C124

22P_4_N_50V

C121

22P_4_N_50V

R166

0_4

1

2

R155

150_4_1%

+V3.3

R157

@2.7K_4

1

2

R159

@2.2K_4

1

2

+V5

VGA_I2C_DAT

CRT_R_Y

CRT_B_Y

R163

150_4_1%

CRT_G_Y

R167

150_4_1%

L4

FB47_6_300MA

C123

10P_4_N_50V

C125

10P_4_N_50V

C122

10P_4_N_50V

C120

10P_4_N_50V

C117

10P_4_N_50V

C119

10P_4_N_50V

C118

22P_4_N_50V

L5

FB47_6_300MA

L6

FB47_6_300MA

L8

FB47_6_300MA

L7

FB47_6_300MA

IO_GND

L3

FB47_6_300MA

D3

BAV99LT1G_SOT23

A

C

K

+V3.3

CRT_VSYNC

CRT_HSYNC

+V3.3

D5

BAV99LT1G_SOT23

A

C

K

+V3.3

D4

BAV99LT1G_SOT23

A

C

K

CRT_VSYNC

CRT_HSYNC

VGA_I2C_DAT_Z

IO_GND

+V3.3

D1

BAV99LT1G_SOT23

A

C

K

Q7

@2N7002_SOT23

D

G

S

CRT_DDCDATA

+V3.3

+V3.3

D2

BAV99LT1G_SOT23

A

C

K

CRT_DDCCLK

VGA_I2C_DAT

CRT_G

VGA_I2C_CK

Figure 4-42: VGA Reference Design