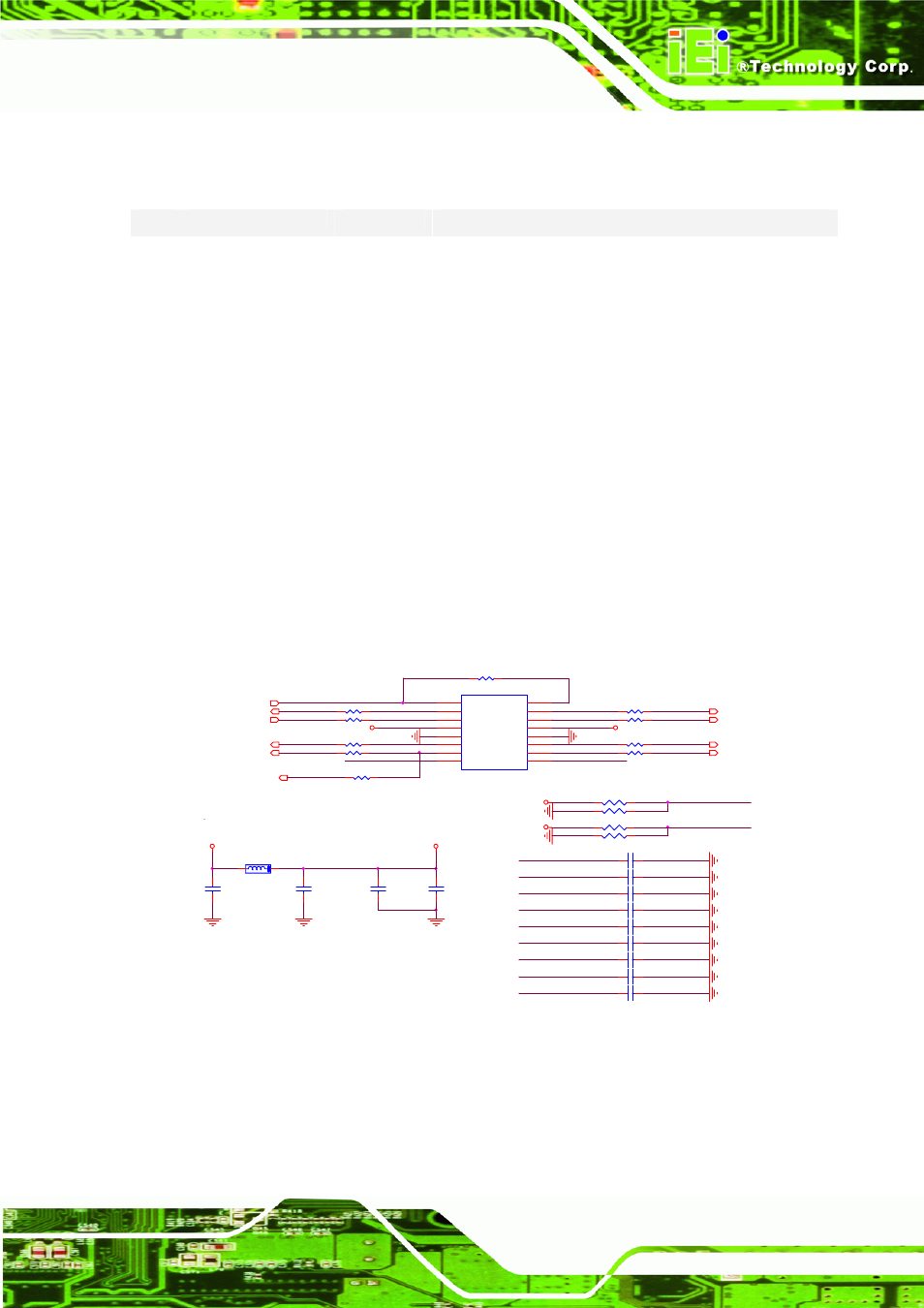

2 clock and reset buffer, Figure 4-34: clock buffer, Table 4-22: lpc interface signal descriptions – IEI Integration ICE-DB-9S User Manual

Page 88: Page 75 ice module

Page 75

ICE Module

Table 4-22: LPC Interface Signal Descriptions

Pin

Signal

I/O

Description

A50 LPC_SERIRQ

I/O 3.3V

CMOS

LPC serialized IRQ.

B3 LPC_FRAME#

O 3.3V

CMOS

LPC frame indicates start of a new cycle or termination

of a broken cycle.

B4

B5

B6

B7

LPC_AD0

LPC_AD1

LPC_AD2

LPC_AD3

I/O 3.3V

CMOS

LPC multiplexed command, address and data.

B8

B9

LPC_DRQ0#

LPC_DRQ1#

I 3.3V

CMOS

LPC encoded DMA/Bus master request.

B10 LPC_CLK

O 3.3V

CMOS

LPC clock output 33MHz.

4.12.2 Clock and Reset Buffer

The ICE module already integrates reset buffer, therefore, the baseboard does not

need reset buffer. For clock buffer, please refer to or integrate with the PCI clock

buffer.

CLK33M_MINICARD

U2

CY2309NZSXC-1H

REF

1

CLKA1

2

CLKA2

3

VDD

4

GND

5

CLKB1

6

CLKB2

7

S2

8

S1

9

CLKB3

10

CLKB4

11

GND

12

VDD

13

CLKA3

14

CLKA4

15

CLKOUT

16

CLK33M_SLOT3

CLK33M_BIOS2

C265

10P_4_N_50V

1

2

CLK33M_SLOT1

CLK33M_SLOT2

CLKBUFFER_S2

CLKBUFFER_S1

C17

0.1U_4_Y_16V

C16

10U_8_X_6V3

C18

0.1U_4_Y_16V

C15

10U_8_X_6V3

+V3.3

FB3

FB30_8_3A

CLK33M_80PORT

C14

10P_4_N_50V

1

2

CLK33M_BIOS2

+V3.3_CLKBUFFER

CLK33M_TPM

C266

10P_4_N_50V

1

2

+V3.3_CLKBUFFER

C13

10P_4_N_50V

1

2

+V3.3_CLK

R65

10K_4

1

2

CLKBUFFER_S2

R67

@10K_4

1

2

R62

10K_4

1

2

CLKBUFFER_S1

+V3.3_CLK

R63

@10K_4

1

2

CLK33M_PCI

C10

10P_4_N_50V

1

2

CLK33M_SLOT1

CLK33M_SLOT3

R45

33_4

1

2

CLK33M_SIO2

C241

10P_4_N_50V

1

2

CLK33M_MINICARD

C11

10P_4_N_50V

1

2

C267

10P_4_N_50V

1

2

CLK33M_MINIPCI

R37

33_4

1

2

R40

33_4

1

2

CLK33M_MINIPCI

C12

10P_4_N_50V

1

2

R38

33_4

1

2

R41

33_4

1

2

R34

@33_4

1

2

CLK33M_SIO2

CLK33M_TPM

R51

33_4

1

2

CLK33M_SLOT2

CLK33M_80PORT

R44

33_4

1

2

R47

33_4

1

2

+V3.3_CLKBUFFER

R48

33_4

1

2

Figure 4-34: Clock Buffer