5 pci express clock buffer, 1 pci express routing guideline, Figure 4-13: pci express clock buffer example – IEI Integration ICE-DB-9S User Manual

Page 59: Ice module page 46

ICE Module

Page 46

Figure 4-12: Mini Card Connector (Refer to www.pcisig.com)

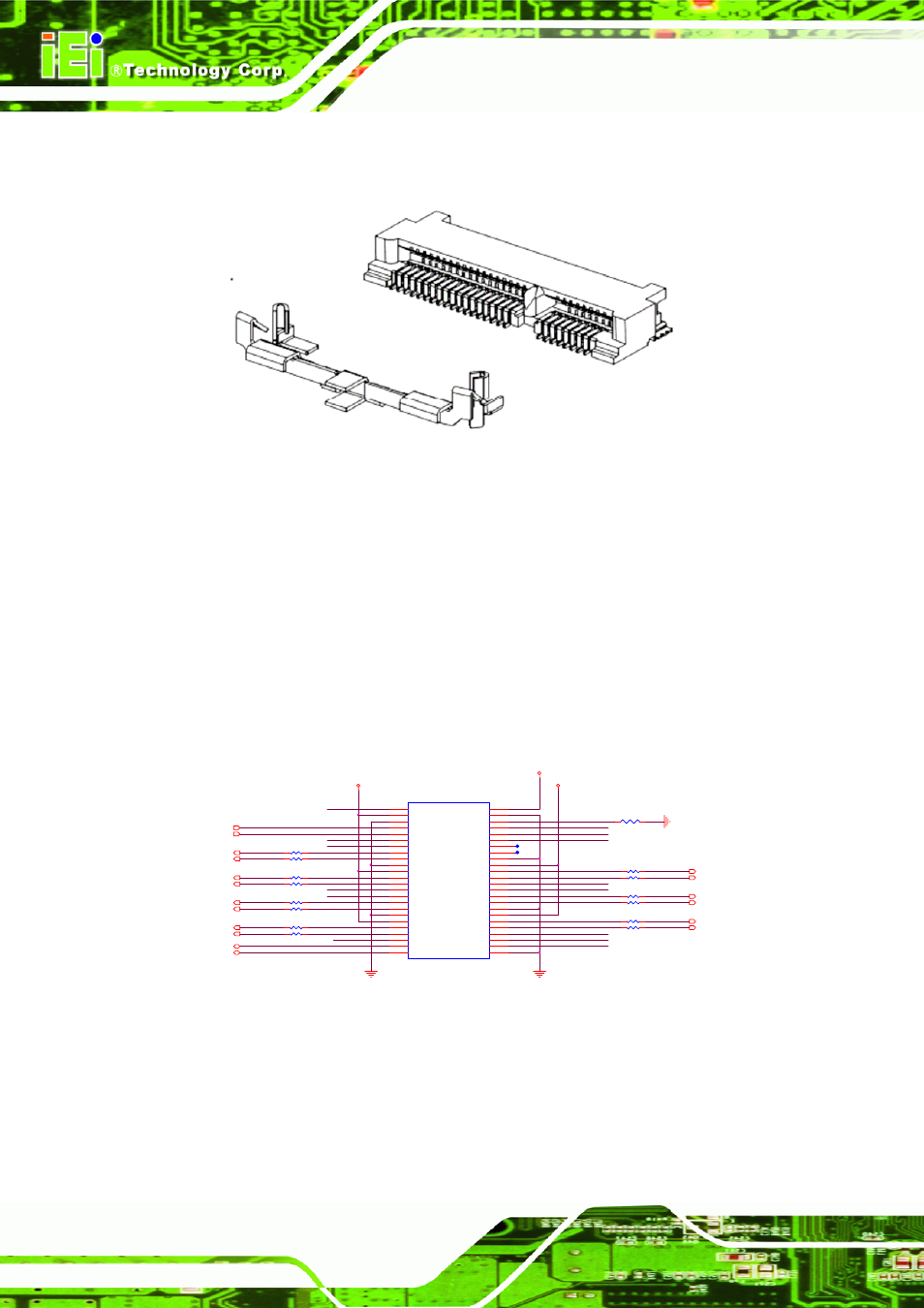

4.2.5 PCI Express Clock Buffer

COM Express only provides a set of 100 MHz Clock for PCI Express Device. When

there are more than one PCI Express modules used on the baseboard, the Clock

Buffer must be used. Please refer to the schematic diagram (Figure 4-13) suggested

by IEI.

CLK100M_PCIEx1_SLOT2+

5

R20

33_4

1

2

CLK100M_PCIEx1_SLOT2-

5

R21

33_4

1

2

CLK100M_PCIEx16_SLOT- 6

CLK100M_PCIEx16_SLOT+ 6

R24

33_4

1

2

CLK_OE_4

R26

33_4

1

2

CLK_OE_3

SMB_DAT

3,5,6,10,11,17,20

SMB_CK

3,5,6,10,11,17,20

CLK_PLL

CLK100M_PCIEx1_SLOT5- 10

CLK100M_PCIEx1_SLOT5+ 10

CLK100M_PCIEx1_SLOT3-

5

CLK100M_PCIEx1_SLOT3+

5

R22

33_4

1

2

R23

33_4

1

2

R113

33_4

1

2

R112

33_4

1

2

+V3.3_CLK

+V3.3_CLK

+V3.3_CLK_A

CLK_OE_6

CLK100M_PCIEx1_SLOT1+

5

CLK_LOCK

CLK_OE_1

R10

475

R114

33_4

1

2

CLK_IREF

R115

33_4

1

2

CLK100M_PCIEx1_SLOT1-

5

CLK100M_PCIEx1_SLOT4+

5

R25

33_4

1

2

CLK100M_PCIEx1_SLOT4-

5

R27

33_4

1

2

CLK100M_PCIE_REF-

3

CLK100M_PCIE_REF+

3

R16

33_4

1

2

CLK_OE_5

R18

33_4

1

2

CLK_OE_2

CLK100M_PCIEx1_SLOT6- 10

CLK100M_PCIEx1_SLOT6+ 10

CLK_HBW#

CLK_SRC_SOP#

CLK_PD#

U1

ICS9DB801

SRC_DIV#

1

VDD01

2

GND01

3

SRC_IN

4

SRC_IN#

5

OE_0

6

OE_3

7

DIF_0

8

DIF_0#

9

GND02

10

VDD02

11

DIF_1

12

DIF_1#

13

OE_1

14

OE_2

15

DIF_2

16

DIF_2#

17

GND03

18

VDD03

19

DIF_3

20

DIF_3#

21

BYPASS#/PLL

22

SCLK

23

SDATA

24

GND05

25

PD#

26

SRC_SOP#

27

HIGH_BW#

28

DIF_4#

29

DIF_4

30

VDD05

31

GND04

32

DIF_5#

33

DIF_5

34

OE_5

35

OE_6

36

DIF_6#

37

DIF_6

38

VDD04

39

OE_INV

40

DIF_7#

41

DIF_7

42

OE_4

43

OE_7

44

LOCK

45

IREF

46

GNDA

47

VDDA

48

CLK_OE_7

TP32

1

CLK_DIV#

TP33

1

CLK_OE_0

Figure 4-13: PCI Express Clock Buffer Example

4.2.5.1 PCI Express Routing Guideline

Please refer to Section 4.1.6