4 peg_enable, 5 pci express test points and probing – IEI Integration ICE-DB-9S User Manual

Page 47

ICE Module

Page 34

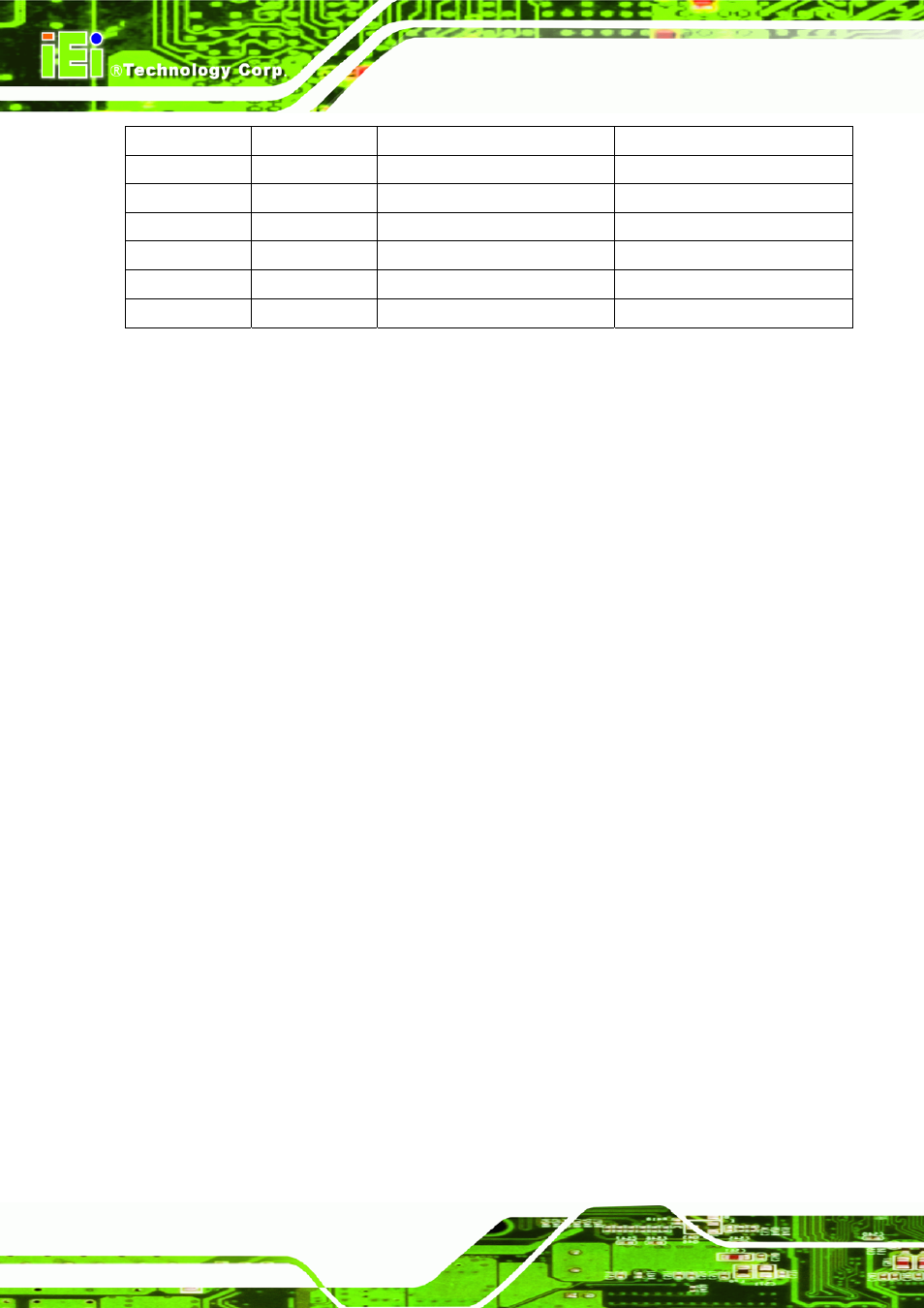

CH7021A

Chrontel

SDTV / HDTV Transmitter

http://www.chrontel.com

CH7308A

Chrontel

LVDS Transmitter http://www.chrontel.com

CH7307C

Chrontel

DVI Transmitter http://www.chrontel.com

CH7312

Chrontel

DVI Transmitter http://www.chrontel.com

CX25905

Conexant

DVI-D / TV / CRT Transmitter http://www.conexant.com

SiL1362/1364 Silicon Image DVI Transmitter

http://www.siliconimage.com

SiL 1390

Silicon Image HDMI Transmitter

http://www.siliconimage.com

4.1.4 PEG_ENABLE#

PEG_ENABLE# is defined on the COM Express connector as a method to configure

the COM Express PCIe lanes 16 through 32 on the C-D connector as a PCI Express

Graphics port, for use with an external graphics device. The usual effect of pulling

PEG_ENABLE# low is to disable the on-Module graphics engine. For some Modules,

it is possible to configure the Module such that the internal graphics engine remains

active, even when the external PEG interface is being used for a Carrier Board

graphics device. This is Module dependent. Check with your vendor. ICE Modules

implement the auto-detect function. So, please reserve this pin for future use.

4.1.5 PCI Express Test Points and Probing

IEI follows the suggestion provided by Intel® to preserve 0-Ω on the baseboard.

Additional test structures were not included in the simulation sweeps that this

guideline is based on. The inclusion of test points and probing structures has the

ability to impact the loss and jitter budgets of a PCI Express interconnect. This is not to

say that they cannot be tolerated. In general, test points and probe structures should

not introduce stubs on the differential pairs or cause significant deviation from the

recommendations given throughout this chapter. Existing vias, pads or pins should be

used wherever possible to accommodate such structures. Careful consideration must

be taken whenever additional probing structures are used.

The PCI Express based specification requires the data eyes to be measured into a

50-Ω resistor terminated to ground. To facilitate the measurement, an additional test

structure may be required on a test board. This test structure should not be included in

a production board because it will affect the overall signal quality and resulting

margins. The three-pad test structure consists of the footprints of two resistors,

perpendicular to each other forming a “L” shape. The resistor package/footprint should