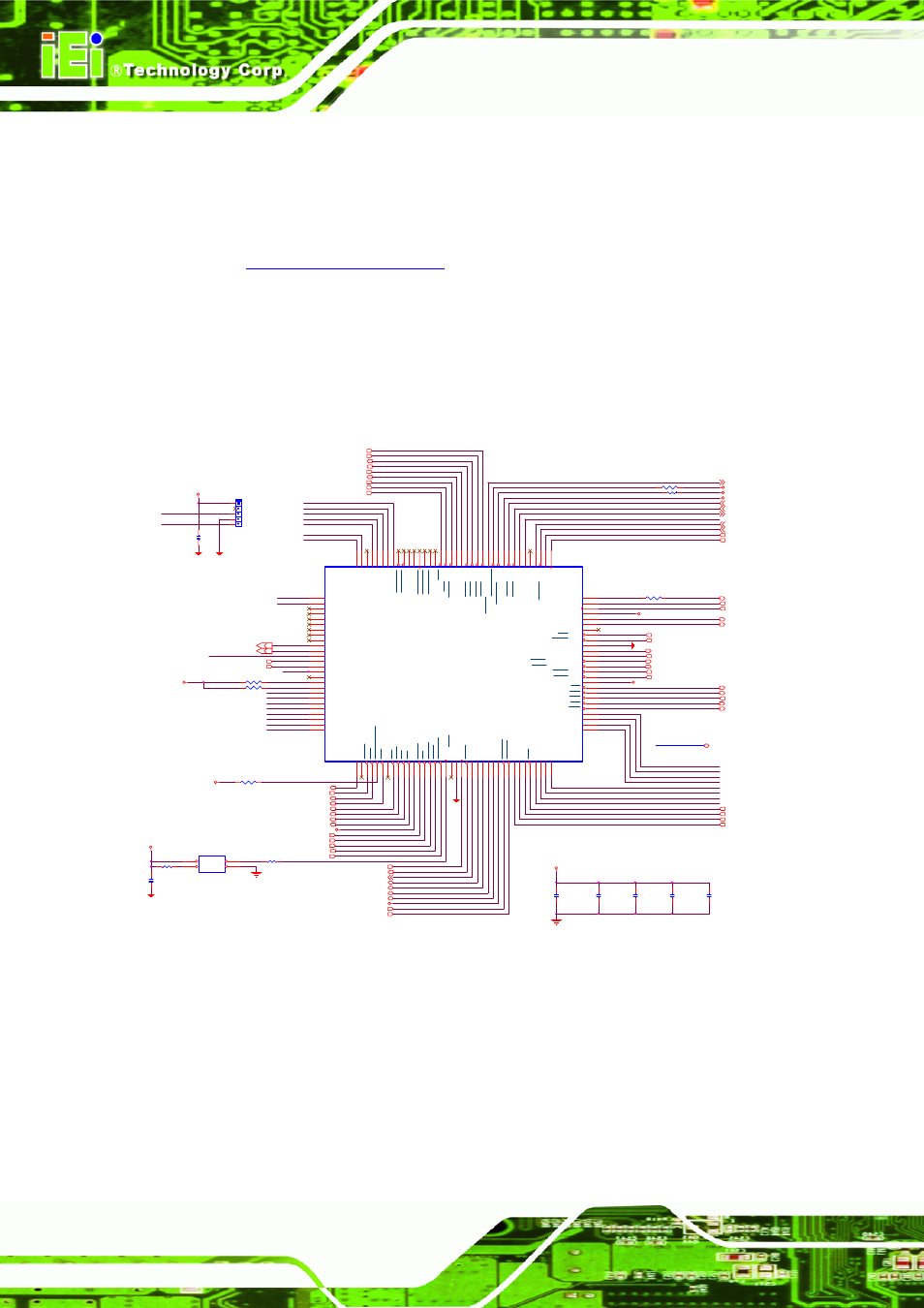

3 lpc superio for legacy io support, 1 keyboard/mouse, Figure 4-35: windbond w83627ehg reference design – IEI Integration ICE-DB-9S User Manual

Page 89: Ir connector

ICE Module

Page 76

4.12.3 LPC SuperIO for Legacy IO Support

Some COM Express modules utilize BIOS that contains built-in support for an external

Winbond W83627HG LPC Super I/O controller that can be implemented on the carrier

board (

The base address for this Super I/O should be

0x2E to be sure that the legacy devices can be initialized by the BIOS. The

implementation of this device on the COM Express carrier board will provide legacy

interfaces such as PS/2 keyboard/mouse, floppy port, two serial ports (COM1 and

COM2) and one parallel port (LPT1). The other functions of this Super I/O controller

are not supported.

WAKE_UP#

3

PCI_RST#

3,5,6,7,8,10,14

+VBAT

C134

0.1U_4_Y _16V

2

1

LPT_SLIN#

15

LPT_PE

15

LPT_AFD#

15

LPT_BUSY

15

LPT_ACK#

15

LPT_STB#

15

LPT_INIT#

15

LPT_ERR#

15

R175

@0_4

1

2

KB_RST#

3

KB_A20GATE 3

C136

0.1U_4_X_10V

2

1

C135

0.1U_4_X_10V

2

1

C137

0.1U_4_X_10V

2

1

C139

0.1U_4_X_10V

2

1

C138

0.1U_4_X_10V

2

1

+V3.3

D-

+V5

UART_TX2

UART_RX2

IR CONNECTOR

IR1

IR_5X1_2.54

1

3

4

5

2

C260

0.1U_4_Y _16V

FDD_WE#

15

FDD_HEAD#

15

FDD_RWC#

15

FDD_DIR#

15

FDD_STEP#

15

FDD_WD#

15

FDD_DSA#

15

FDD_RDATA#

15

FDD_DSKCHG#

15

FDD_MOA#

15

FDD_INDEX#

15

FDD_TRACK0#

15

FDD_WP#

15

+V3.3

LPC_FRAME#

3,5,11,14,20

LPC_AD0

3,5,11,14,20

LPC_AD2

3,5,11,14,20

LPC_DRQ#0

3,11

LPC_AD1

3,5,11,14,20

LPC_AD3

3,5,11,14,20

CLK33M_LPC

3

R180

4.7K

Y 1

OSC48MHZ_SMD

EN

1

GND

2

VDD

4

OUT

3

HM_VREF

VTIN3

+5VIN

+3.3VIN

+12VIN

VIN1

VIN2

MINICARD_DISABLE# 5

D+

R174

10K_4

SIO_DOUT0

SIO_DOUT2

SIO_DOUT1

SIO_DIN0

SIO_DIN2

SIO_DIN3

SIO_DIN1

LPT_PD3

LPT_PD0

LPT_PD2

LPT_PD4

FAN_IO1

20

FAN_PWM2

20

FAN_IO2

20

CASEOPEN#

FAN_PWM1

20

LPT_PD6

LPT_PD1

LPT_PD7

IOAVCC

LPT_PD5

CLK48M_SIO1

SIO_SMI-

R179

33_4

1

2

+V3.3_DUAL

PM_PWRBTN# 3

PM_SLP_S3#

3

SERIRQ

3,11,14

PANSWIN

21

+V3.3_DUAL

PS_ON#

21,23

PWROK_SIO

3

W83627EHG

U13

W83627EHG_PQFP128

D

R

V

D

E

N

0

1

G

P

2

3/

S

C

K

2

IN

D

E

X

3

M

O

A

4

GP10/GPSA1

128

CPUTIN

103

SY STIN

104

VID5

105

VID4

106

VID3

107

VID2

108

VID1

109

VID0

110

AUXFANIN0

111

CPUFANIN0

112

SY SFANIN

113

AVCC3

114

CPUFANOUT0

115

SY SFANOUT

116

AGND

117

BEEP/SI

118

GP21/CPUFANIN1/MSI

119

GP20/CPUFANOUT1/MSO

120

GP17/GPSA2

121

GP16/GPSB2

122

GP15/GPY1

123

GP14/GPY2

124

GP13/GPX2

125

GP12/GPX1

126

GP11/GPSB1

127

H

M

_

S

M

I

/

O

V

T

5

D

S

A

6

A

U

X

F

A

N

O

U

T

0

7

D

IR

8

S

T

E

P

9

W

D

1

0

W

E

1

1

V

C

C

3

_

1

1

2

T

R

A

K

0

1

3

W

P

1

4

R

D

A

T

A

1

5

H

E

A

D

1

6

D

S

K

C

H

G

1

7

IO

C

L

K

1

8

G

P

2

2/

S

C

E

1

9

V

S

S

_

1

2

0

P

C

IC

L

K

2

1

L

D

R

Q

2

2

S

E

R

IR

Q

2

3

L

A

D

3

2

4

L

A

D

2

2

5

L

A

D

1

2

6

L

A

D

0

2

7

V

C

C

3

_

2

2

8

L

F

R

A

M

E

2

9

L

R

E

S

E

T

3

0

S

L

C

T

3

1

P

E

3

2

B

U

S

Y

3

3

A

C

K

3

4

P

D

7

3

5

P

D

6

3

6

P

D

5

3

7

P

D

4

3

8

PD3

39

PD2

40

PD1

41

PD0

42

SLIN

43

INIT

44

ERR

45

AFD

46

STB

47

VCC3_3

48

CTSA/GP67

49

DSRA/GP66

50

RTSA/GP65/HEFRAS

51

DTRA/GP64/PENROM

52

SINA/GP63

53

SOUTA/GP62/PENKBC

54

VSS_2

55

DCDA/GP61

56

RIA/GP60

57

SO/AUXFANIN1

58

GA20M

59

KBRST

60

3VSB

61

KCLK/GP27

62

KDAT/GP26

63

GP37

64

M

C

L

K

6

5

M

D

A

T

/G

P

2

4

6

6

P

S

O

U

T

/G

P

5

7

6

7

P

S

IN

/G

P

5

6

6

8

G

P

3

6

6

9

G

P

5

5/

S

U

S

L

E

D

7

0

P

W

R

O

K

/G

P

5

4

7

1

P

S

O

N

/G

P

5

3

7

2

S

U

S

B

/G

P

5

2

7

3

V

B

A

T

7

4

R

S

M

R

S

T

/G

P

5

1

7

5

C

A

S

E

O

P

E

N

7

6

G

P

5

0/

W

D

T

O

/E

N

_

V

R

M

1

0

7

7

C

T

S

B

/G

P

4

7

7

8

D

S

R

B

/G

P

4

6

7

9

R

T

S

B

/G

P

4

5

8

0

D

T

R

B

/G

P

4

4

8

1

S

IN

B

/I

R

R

X

8

2

S

O

U

T

B

/I

R

T

X

8

3

D

C

D

B

/G

P

4

1

8

4

R

IB

/G

P

4

0

8

5

P

M

E

8

6

G

P

3

5

8

7

G

P

3

4/

R

S

T

O

U

T

4

8

8

S

D

A

/G

P

3

3/

R

S

T

O

U

T

3

8

9

S

C

L/

G

P

3

2/

R

S

T

O

U

T

2

9

0

G

P

3

1

9

1

G

P

3

0

9

2

R

S

T

O

U

T

1

9

3

R

S

T

O

U

T

0

9

4

V

IN

4

9

5

V

IN

3

9

6

V

IN

2

9

7

V

IN

1

9

8

V

IN

0

9

9

C

P

U

V

C

O

R

E

1

0

0

V

R

E

F

1

0

1

A

U

X

T

IN

1

0

2

WDTO : 6F02

DIO in : 6F08

DIO out : 6F09

SIO_DOUT3

LPT_SLCT

15

+V3.3

+V5

+V3.3

R177

1K_4_1%

R176

4.7K_4

SIO_WDT#

21

SUS_LED

R178

10K_4

+V3.3_DUAL

+V3.3

R173

10M_4

UART_DSR#1 15

UART_RX1

15

UART_DCD#1 15

UART_CTS#1 15

UART_DTR#1 15

UART_TX1

15

UART_RI#1

15

UART_RTS#1 15

UART_RX2

16

UART_DCD#2

16

UART_CTS#2

16

UART_DTR#2

16

UART_TX2

16

UART_DSR#2

16

UART_RI#2

16

UART_RTS#2

16

+VBAT

LPT_PD[7..0]

15

LPT_PD[7..0]

VTIN1

KB_CLK#

15

MS_DAT#

15

MS_CLK#

15

KB_DAT#

15

Figure 4-35: Windbond W83627EHG Reference Design

4.12.3.1 Keyboard/Mouse

The following figures display reference circuitries for the legacy I/O interfaces such as

PS/2 keyboard/mouse, RS-232 serial port, parallel port and floppy port connected to

the Winbond W83627HG Super I/O controller. The PS/2 connector has to be powered