Figure 4-6: express card slot example, Table 4-6: express card pin definition, Page 41 ice module – IEI Integration ICE-DB-9S User Manual

Page 54

Page 41

ICE Module

PCIE_WAKE_UP#

Express Card connector

E_Card_CON1

GND4

P26

PETp0

P25

PETn0

P24

GND3

P23

PERp0

P22

PERn0

P21

GND2

P20

REFCLK+

P19

REFCLK-

P18

CPPE#

P17

CLKREQ#

P16

+3.3V2

P15

+3.3V1

P14

PERST#

P13

+3.3VAUX

P12

WAKE#

P11

+1.5V

P10

SMB_DATA

P9

SMB_CLK

P8

RESERVED3

P7

RESERVED2

P6

RESERVED1

P5

CPUSB#

P4

USB_D+

P3

USB_D-

P2

GND1

P1

H

1

H

1

H

2

H

2

+V3.3_ExpressCard

+V3.3SB_ExpressCard

LED7

LEDRED_8_2

A

C

R360

470_6

PCIE_TX2-

3

PCIE_TX2+

3

EC10

@150U_TNC_SMD_6.3V

PCIE_RX2+

3

PCIE_RX2-

3

+V3.3_ExpressCard

CLK100M_PCIEx1_SLOT3+

4

CLK100M_PCIEx1_SLOT3-

4

+V1.5_ExpressCard

CPPE#

CB_RESET#

3,6,10,11,14,20

C26

10U_8_X_6V3

CPUSB#

+V3.3_ExpressCard

SMB_DAT

3,4,6,10,11,17,20

SMB_CK

3,4,6,10,11,17,20

L2

COMCHOKE_8_USB

1

4

2

3

R73

10K_4

1

2

R74

10K_4

1

2

+V3.3SB_ExpressCard

USB6+

3

USB6-

3

C29

0.1UF

Q1

GS1117-SOT223

V_IN

I

G

N

D

G

V_OUT

O

V_OUT1

4

R75

124 1%-RS

R76

24.9 1%-RS

+V1.5

+V3.3

VCC1.5/1A

+V3.3

+V3.3SB_ExpressCard

EC9

@150U_TNC_SMD_6.3V

+V1.5_ExpressCard

CPPE#

C35

0.1U_4_Y_16V

+V3.3_ExpressCard

C37

0.1U_4_Y_16V

LED6

LEDRED_8_2

A

C

R350

470_6

+V3.3_ExpressCard

TP41

1

+V3.3

TP42

1

+V1.5_ExpressCard

C38

0.1U_4_Y_16V

+V3.3SB_ExpressCard

PERST#

C28

10U_8_X_6V3

+V1.5

TPS2231

TPS2231

U3

SYSRST#

1

SHDN#

2

STBY#

3

3.3VIN1

4

3.3VIN2

5

3.3VOUT1

6

3.3VOUT2

7

PERST#

8

NC

9

GND

10

OC#

20

RCLKEN

19

AUXIN

18

AUXOUT

17

1.5VIN2

16

1.5VIN1

15

1.5VOUT2

14

1.5VOUT1

13

CPPE#

12

CPUSB#

11

PERST#

CPUSB#

+V3.3_DUAL

+V3.3_ExpressCard

+V3.3

C36

10U_8_X_6V3

+V1.5_ExpressCard

C30

10U_8_X_6V3

C27

0.1U_4_Y_16V

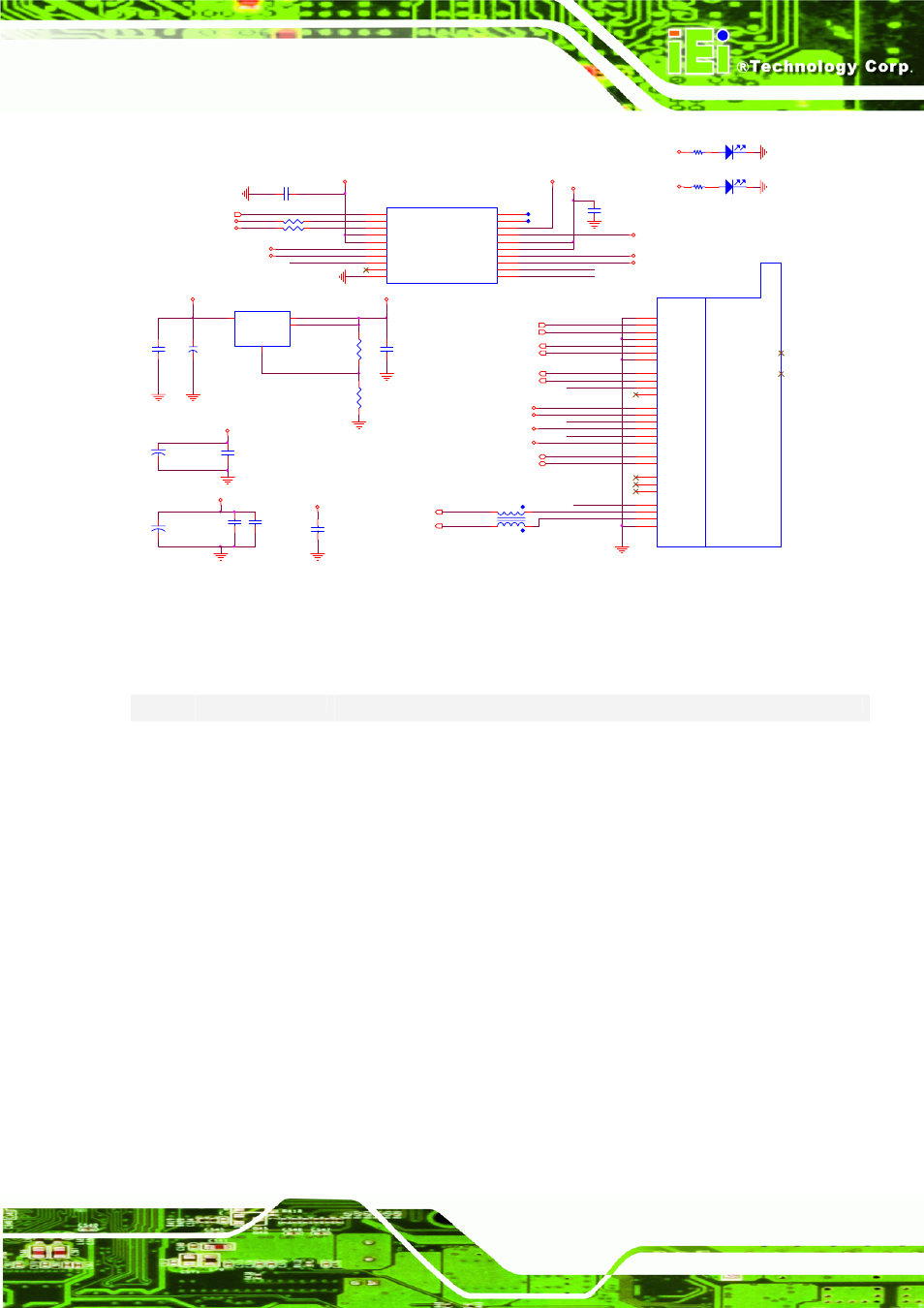

Figure 4-6: Express Card Slot Example

Table 4-6: Express Card Pin Definition

Pin

Signal

I/O

Description

1

GND

P

Ground

2

USB_D-

I/O USB

USB Serial Data Interface differential pair, negative signal

3

USB_D+

I/O USB

USB Serial Data Interface differential pair, positive signal

4

CPUSB#

I 3.3V

USB Interface presence detected

5

RSVD

Reserved

6

RSVD

Reserved

7

SMBCLK

I/O 3.3V

System Management Bus Clock

8

SMBDATA

I/O 3.3V

System Management Bus Data

9

+1.5V

P 1.5V

Secondary voltage source, 1.5V

10

+1.5V

P 1.5V

Secondary voltage source, 1.5V

11

WAKE#

I 3.3V

Request that the host interface return to full operation and

respond to PCIe

12

+3.3VAUX

P 3.3V

Auxiliary voltage source, 3.3V

13

PERST#

I 3.3V

PCI Express Reset

14

+3.3V

P 3.3V

Primary voltage source, 3.3V

15

+3.3V

P 3.3V

Primary voltage source, 3.3V

16

CLKREQ#

I 3.3V

Request that REFCLK be enabled

17

CPPE#

I 3.3V

PCI Express interface presence detect

18 REFCLK-

I

PCIe

PCI Express reference clock differential pair, negative

signal

19

REFCLK+

I PCIe

PCI Express reference clock differential pair, positive signal

20

GND

P

Ground

21

PERn0

I/O PCIe

PCI Express Receiver differential pair negative signal

22

PERp0

I/O PCIe

PCI Express Receiver differential pair positive signal