Teledyne LeCroy Kibra DDR User Manual

Page 66

Teledyne LeCroy

Recording Options Setup

64

Kibra DDR Protocol Analyzer User Manual

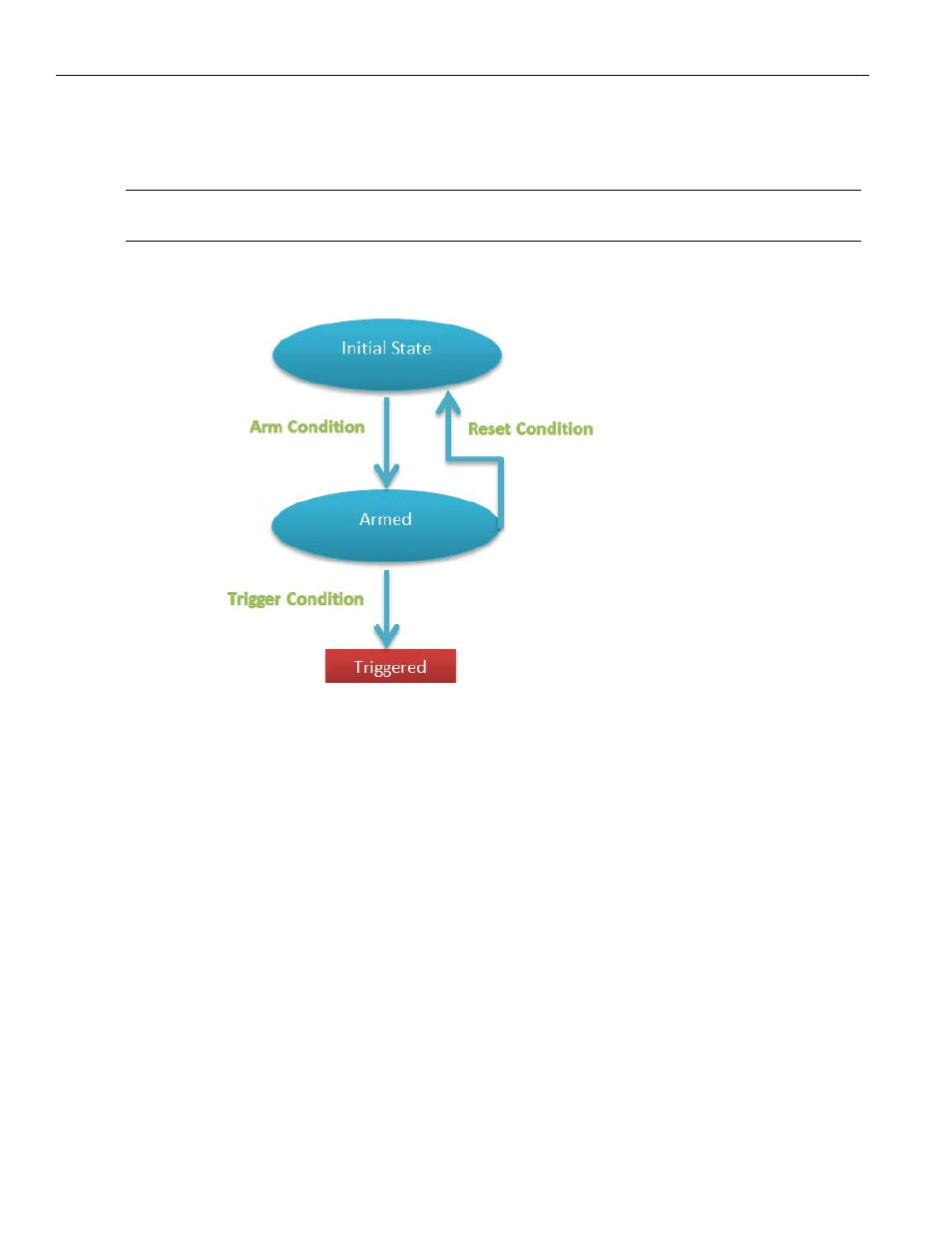

When this condition occurs, the sequence trigger should see an arm condition

before the trigger.

Trigger condition: This condition is the condition that causes an analyzer trigger.

Note:

In any case where the reset or trigger is to occur after some number of clocks (nClk), the number

entered should be 3 or larger.

The figure below shows the trigger sequence.

Figure 2.33: Sequence Trigger Flow of Condition

The following parameters should be carefully considered in defining sequence conditions

for obtaining correct trigger results:

All the conditions are based on the individual signals (see

), where the values selected are AND'ed with each other to get a result.

For example, if you want to trigger on an MRS on Chip Select 1, you would set

the Command Value to "Low Low Low" and the CS1# to "Low", all other CS#'s at

"Don't Care". Alternatively if you want to trigger on any case where the RAS#

CAS# and WE# are "Low", you would leave all the CS#'s at "Don't Care".

For chip select signal, an “Any Chip Select” option is provided. This allows you

define an “or” condition on all ranks. This means that if other signal conditions

occur on any other chip select, the engine considers it as a matched condition,

regardless of the chip select. However, at least one chip select should be active

to match the condition.

Any signal can be triggered with different transitions and states as follow:

High

Low

Rising Edge

Falling Edge

Either Edge