4 v04 - tfaw four activate window – Teledyne LeCroy Kibra DDR User Manual

Page 162

Teledyne LeCroy

DDR3 and DDR4 JEDEC Timing Violations Summary

160

Kibra DDR Protocol Analyzer User Manual

5.1.3

V03 - tRRD ACTIVATE to ACTIVATE command period (DDR3 different bank,

same rank) (DDR4 - same bank group)

The minimum interval between Activate of one Bank and the next Activate in the same

Rank is specified to ensure SDRAM has enough time to activate the first row into the

Sense Amps and settle before the next Row is activated. Also known as the “row‐to‐row

delay” this interval allows the necessary latency to process the pending command. For

DDR4, this measurement is for the Same Bank Group, and is denoted as tRRD‐SBG.

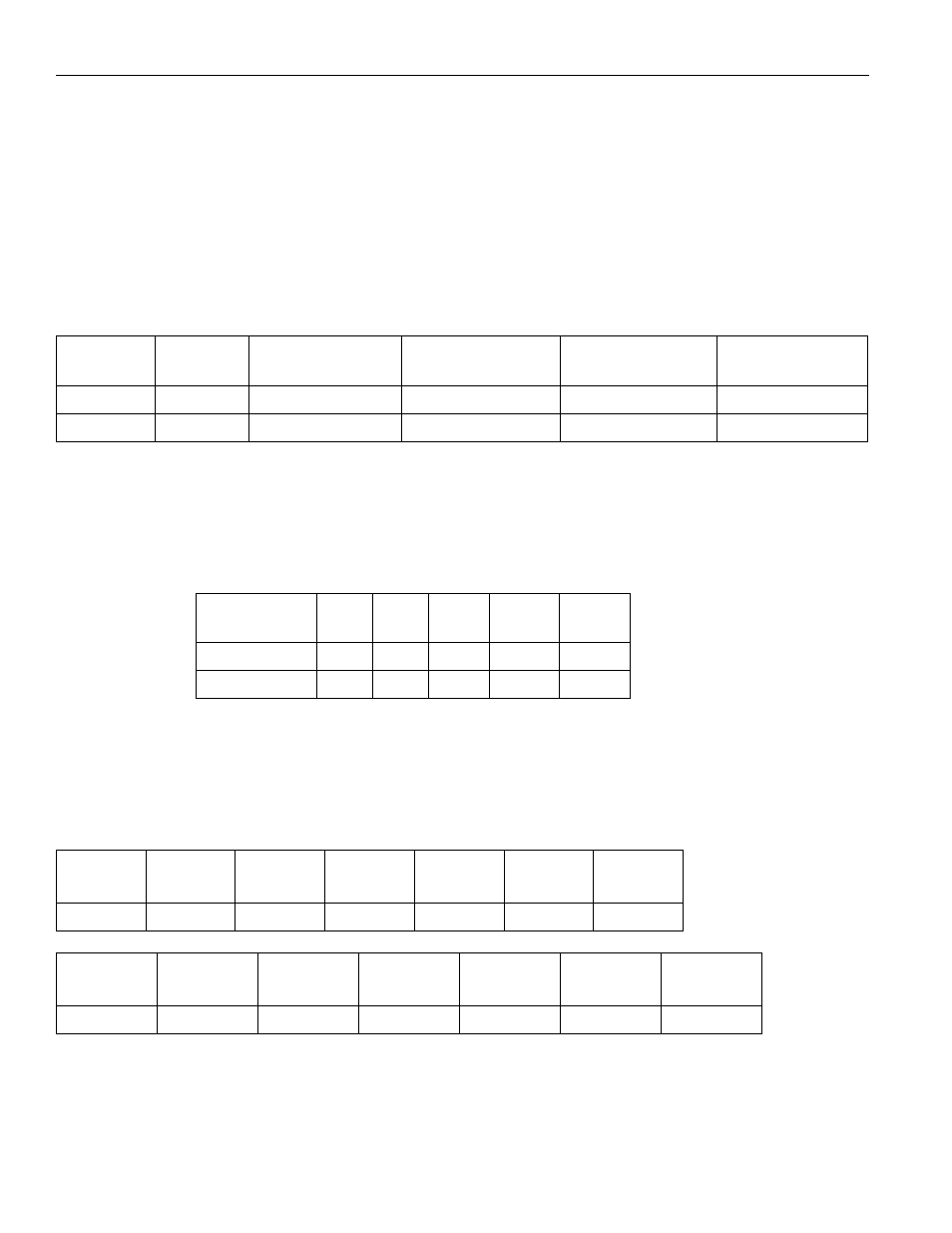

5.1.4

V04 - tFAW Four Activate Window

Intended to limit thermal overload, the controller is allowed to Activate four different

Banks with in this time window. Activating a 5th Bank within this time window (30 ‐ 50ns)

will cause a violation. Activating the 5th Bank on the exact expiration time is valid.

5.1.5

V05 - tRCDx ACTIVATE to internal read or write delay (same bank)

The minimum interval between Activate and Internal Read or Write is specified to allow

sense amps time to open the selected row. For systems with Additive Latency, tRCDx =

tRCD[spec] ‐ AL.

Speed

Grade

Page Size

800

1066

1333

1600

Min (ns)

1KB

max(4nCK, 10ns)

max(4nCK, 7.5ns)

max(4nCK, 6ns)

max(4nCK, 6ns)

Min (ns)

2KB

max(4nCK, 10ns)

max(4nCK, 10ns)

max(4nCK, 7.5ns)

max(4nCK, 7.5ns)

Speed Grade

Page

Size

800

1066

1333

1600

Min (ns)

1KB

40

37.5

30

30

Min (ns)

2KB

50

50

45

40

Speed

Grade

800D

(5‐5‐5)

800E

(6‐6‐6)

1066E

(6‐6‐6)

1066F

(7‐7‐7)

1066G

(8‐8‐8)

1333F

(7‐7‐7)

Min (ns)

12.5

15

11.25

13.125

15

10.5

Speed

Grade

1333G

(8‐8‐8)

1333H

(9‐9‐9)

1600G

(8‐8‐8)

1600H

(9‐9‐9)

1600J

(10‐10‐10)

1600K

(11‐11‐11)

Min (ns)

12

13.5

10

11.25

12.5

13.75