35 v36 - tcke clock enable minimum pulse width, 36 v37 - tpd power down entry to power down exit, 38 v39 - tzqoper zqcl to a valid command – Teledyne LeCroy Kibra DDR User Manual

Page 168

Teledyne LeCroy

DDR3 and DDR4 JEDEC Timing Violations Summary

166

Kibra DDR Protocol Analyzer User Manual

5.1.35

V36 - tCKE Clock Enable minimum pulse width

Defined as the minimum pulse width for Clock Enable. When CKE drops (to signal Power

Down entry), it must stay low for the time defined.

5.1.36

V37 - tPD POWER DOWN ENTRY to POWER DOWN EXIT

Defined as the minimum interval between Power Down Entry to Power Down Exit. This is

calculated in a range with minimum of tCKE and maximum 9 * tREFI.

5.1.37

V38 - tZQCS SHORT Calibration Sequence to a Valid Command

Defined as the minimum interval between Short Calibration Sequence command to next

valid command. This is calculated as max(64nCK, 80ns) for all speed bins.

5.1.38

V39 - tZQOper ZQCL to a Valid Command

Defined as the minimum interval between long Calibration Sequence command to next

valid command. This is calculated as max(256nCK, 320ns) for all speed bins.

5.1.39

V40 - tZQinit First ZQCL after Reset to a Valid Command

Defined as the minimum interval between the first Long Calibration Sequence (ZQCL)

command after reset to next valid command. This is calculated as max(512nCK, 640ns)

for all speed bins.

5.1.40

V41 - tMRD MODE Register Set to Mode Register Set

Mode Register delay is required to complete the write operation to the mode register

and is the minimum time required between two MRS commands. This is calculated as 4

nCK for all speed bins.

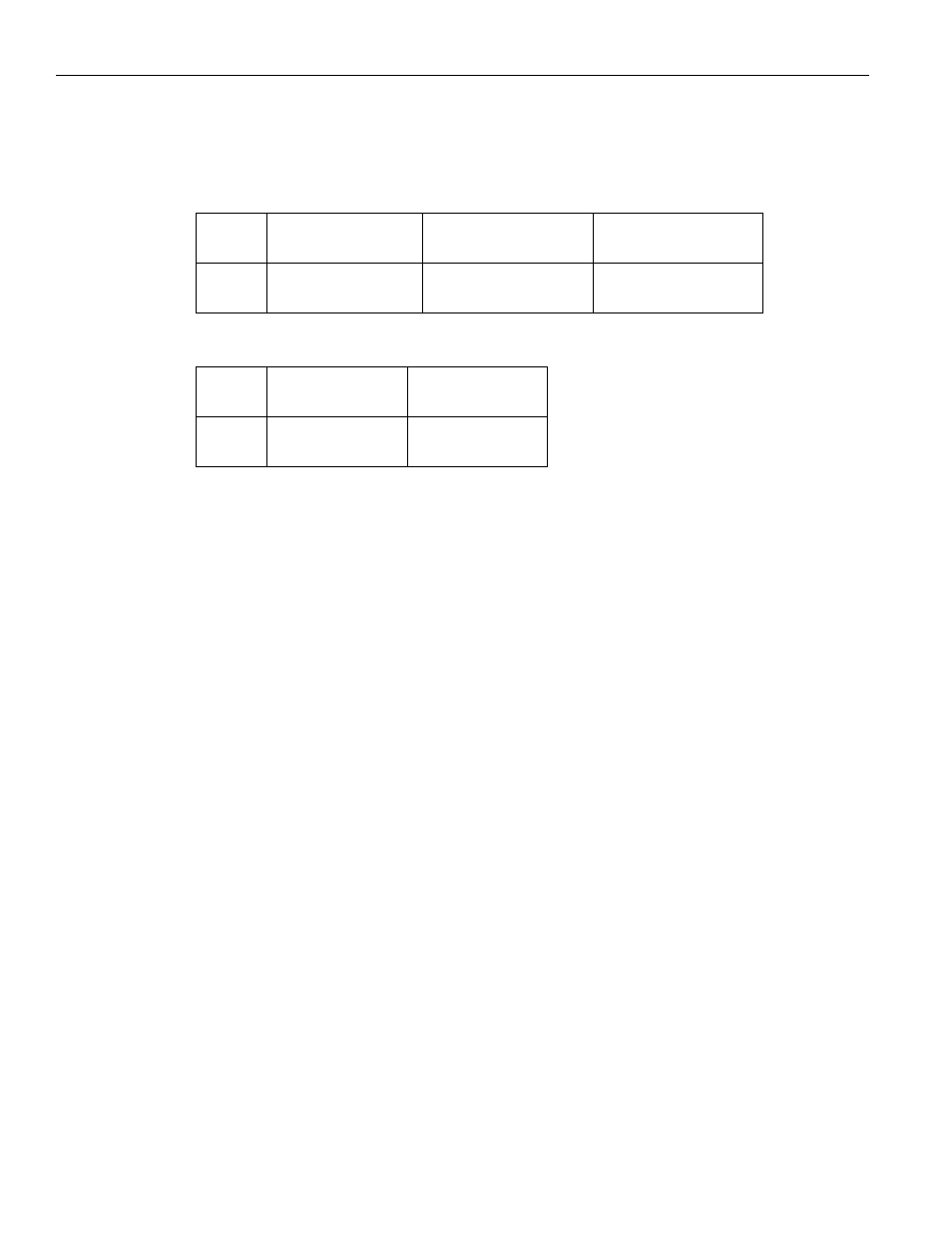

Speed

Grade

800

1066

1333

Max

(nCK)

Max (3nCK, 7.5ns)

max(3nCK, 5.625ns)

max(3nCK, 5.625ns)

Speed

Grade

1600

1866

Max

(nCK)

max(3nCK, 5ns)

max(3nCK, 5ns)