NEC NEAX NDA-24349 User Manual

Page 54

Chapter 3 System Highlights

Page 3- 2

NEAX2000 IPS

Request For Proposal (RFP) Reference Guide

NDA-24349 Issue 4

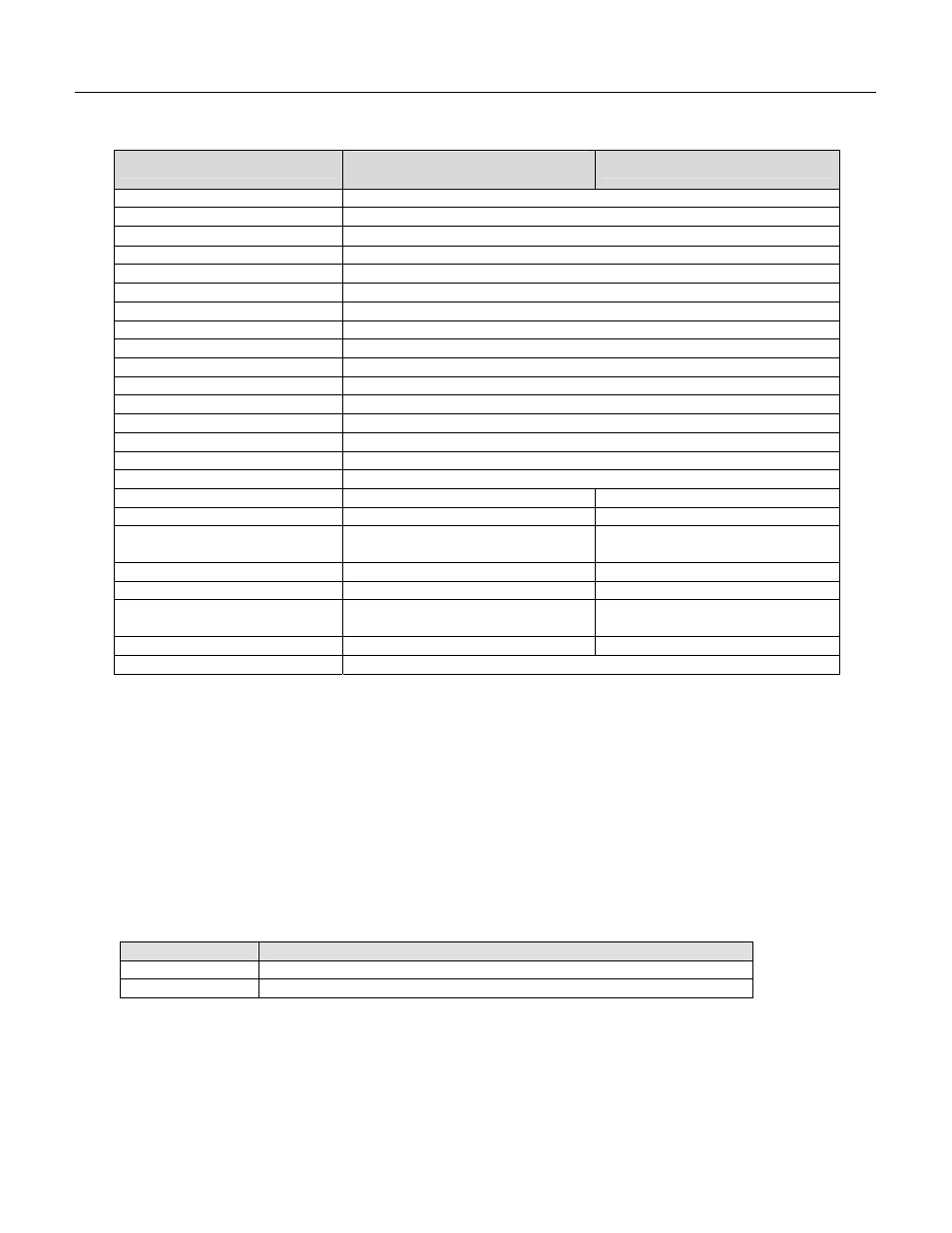

Major specifications and functionality of the NEAX IPS MPs are shown below

:

Item

PN-CP24-B

PN-CP27-A

PN-CP31-A

Central Processing

ElanSC520

System Memory

Flash ROM (8MB), SDRAM (32MB)

Network Switching

1,024

× 1,024 Time Division Switch

3-Way Conference

16 sets of 3-way conference circuitry

DTMF Signal Sender

32 circuits (digit 0 to 9, *, and # are generated)

Music-on-Hold

10 types are available Note

Mini Jack

1 for External Music Source for Music on Hold Note

Audible Tone Generator (DTG)

Available

Phase Lock Oscillator (PLO)

2 ports (Source/Receiver)

Built-in SMDR

Available

Built-in MCI

Available

Built-in FP0

Available

BS00 Function

Available

DTMF Receiver

4 circuits

AP01 Function

Available

Built-in DRS

Available

MAT Interface

---

---

Direct Connection

1 port

1 port

Remote Connection

w/Built-in MODEM

1 port

Not Available

External Alarm Indication

MJ and MN

MJ only

DAT

2circuits (120 seconds per circuit) Not Available

DK00

2 circuits (relay drive x1,

external key scan x1)

Not Available

Application Key Program

In EPROM

In Flash ROM

Built-in DRS (Device Registration Server)

Note:

In case of D

term

IP, the synthesized melody is provided built into IP adapter on the phone

Firmware Processor (FP)

Firmware Processors (FP) are required when more than two PIMs/Modular Chassis (MC) are used.

The FP provides supervision and status analysis of line/trunk ports, which reside in the MC or PIM.

The FP provides the bus interface for I/O Bus, PCM Bus, and Alarm Bus in a multiple-PIM

configuration. The major specifications of the FP are shown below:

Central Processor Unit: 16-bit (25 MHz)

Memory: Program Area (384 kb), Work Area (384 kb)

BS01

Function

Name Code

Remarks

PN-CP15

Firmware Processor Card for use with the NEAX 2000 IPS.

PN-CP19 Firmware

Processor

Card for use with the NEAX 2000 IPS

DM

.