Single holding register change loopback test – Yaskawa MP920 Communications Module User Manual

Page 257

Appendix B 218IF Messages

B.1.2 MEMOBUS Binary Mode

B-8

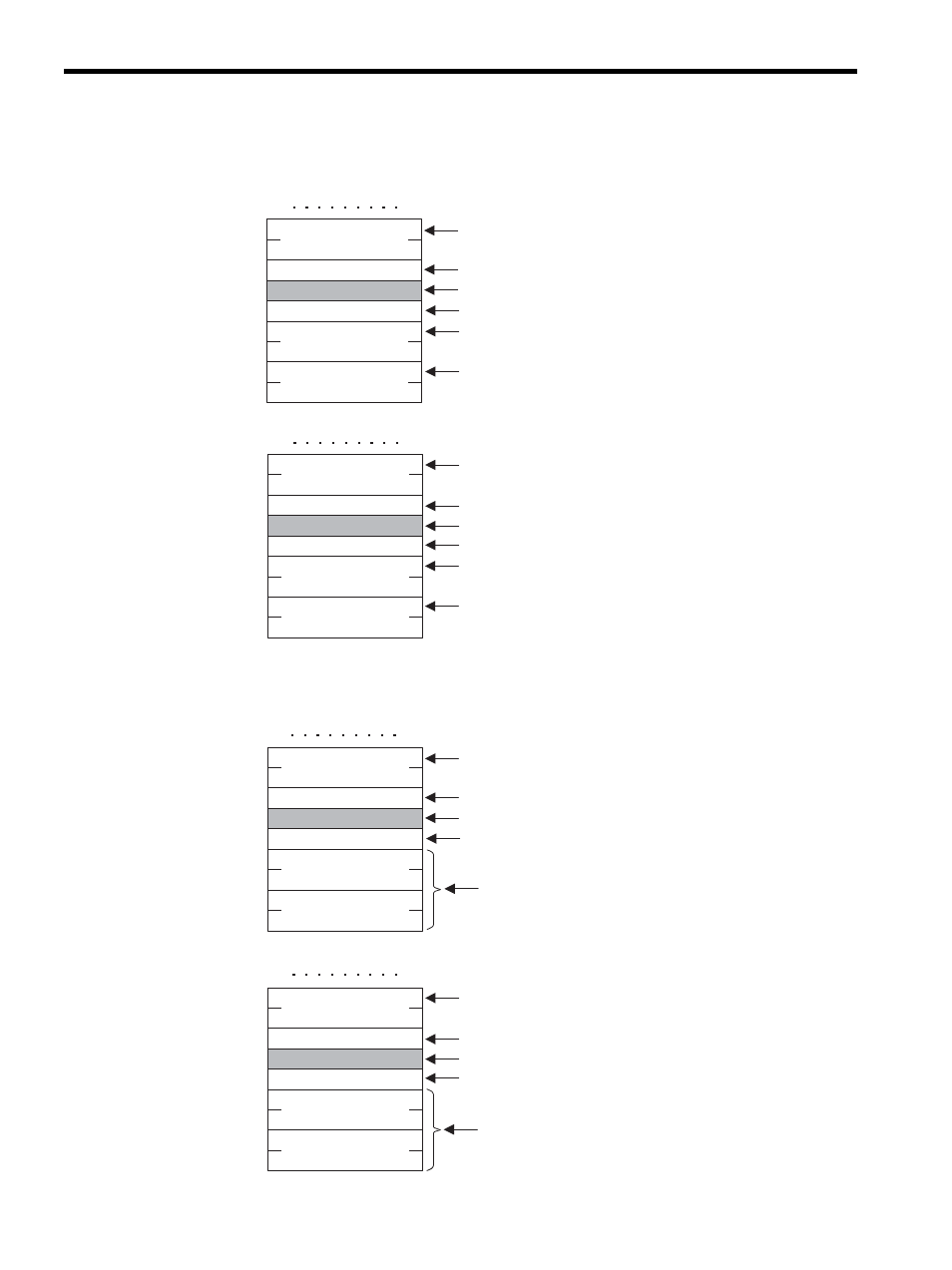

Single Holding Register Change

Loopback Test

MFC: 20H

SFC: 06H

Length: 07H

CPU No.

Set the command length.

Command

Always 20H.

The SFC number is 06H when a single holding register is written.

Set 4 bits each for the destination CPU number and the source

CPU number.

Set the address of the single holding to be changed.

Set the contents to be changed in the single holding registers.

(L)

(H)

Reference No.

Register data

(L)

(H)

(L)

(H)

7

0

MFC: 20H

SFC: 06H

Length: 07H

CPU No.

Set the command length.

Response

Always 20H.

The same SFC number as that specified in the command is

returned.

Set 4 bits each for the destination CPU number and the source

CPU number.

The address of the changed single holding register is returned.

The changed single holding register contents is returned.

(L)

(H)

Reference No.

Register data

(L)

(H)

(L)

(H)

7

0

MFC: 20H

SFC: 08H

Length: 07H

0000H

AAAAH

CPU No.

Set the command length.

Command

Always 20H.

The SFC number is 08H with the loopback test.

Set 4 bits each for the destination CPU number and the source

CPU number.

Set the test data.

(L)

(H)

Data

Test code

7

0

MFC: 20H

SFC: 08H

Length: 07H

0000H

AAAAH

CPU No.

Set the command length.

Response

Always 20H.

The same SFC number as that specified in the command is returned.

Set 4 bits each for the destination CPU number and the source CPU

number.

If the test is completed normally, the same data will be returned

as for the command.

(L)

(H)

Data

Test code

7

0