Table 6-65, Default boot spi flash write enable, Maps and registers – Artesyn ATCA-7365 Installation and Use (May 2014) User Manual

Page 211

Maps and Registers

ATCA-7365 Installation and Use (6806800K65M)

211

Write protection status signals for the Boot SPI flashes are determined by external switch

settings SW1.1and SW1.2. Software can overwrite the status of the write protection status by

writing a magic word to the Boot SPI Flash Write Enable Registers.

4

TSOP or PLCC Boot select. Signal BOOT_TSOP.

0: TSOP selected

1: PLCC selected

Ext.

0: SW1.3 OFF

1: SW1.3 ON

LPC: r

5

Manual Boot Flash select enable. Signal

BOOT_SEL_EN_.

0: Signal BOOT_SELECT selects active boot flash

1: Switch SW3.2 selects the active Boot Flash.

Ext.

0: SW3.1 OFF

1: SW3.1 ON

LPC: r

6

Manual Boot Flash select. Signal BOOT_DEFAULT.

Used when SW3.1 is ON:

0: Selects Default Boot SPI Flash.

1: Selects Recover Boot SPI Flash.

Ext.

0: SW3.2 OFF

1: SW3.2 ON

LPC: r

7

IPMC signal BOOT_SELECT. Boot Flash Select.

0: Selects Default Boot SPI Flash

1: Selects Recovery Boot SPI Flash

Ext.

LPC: r

1. The default is latched from SW1.1 when ICH_PLTRST_ is deasserted.

2. The default is latched from SW1.2 when ICH_PLTRST_ is deasserted

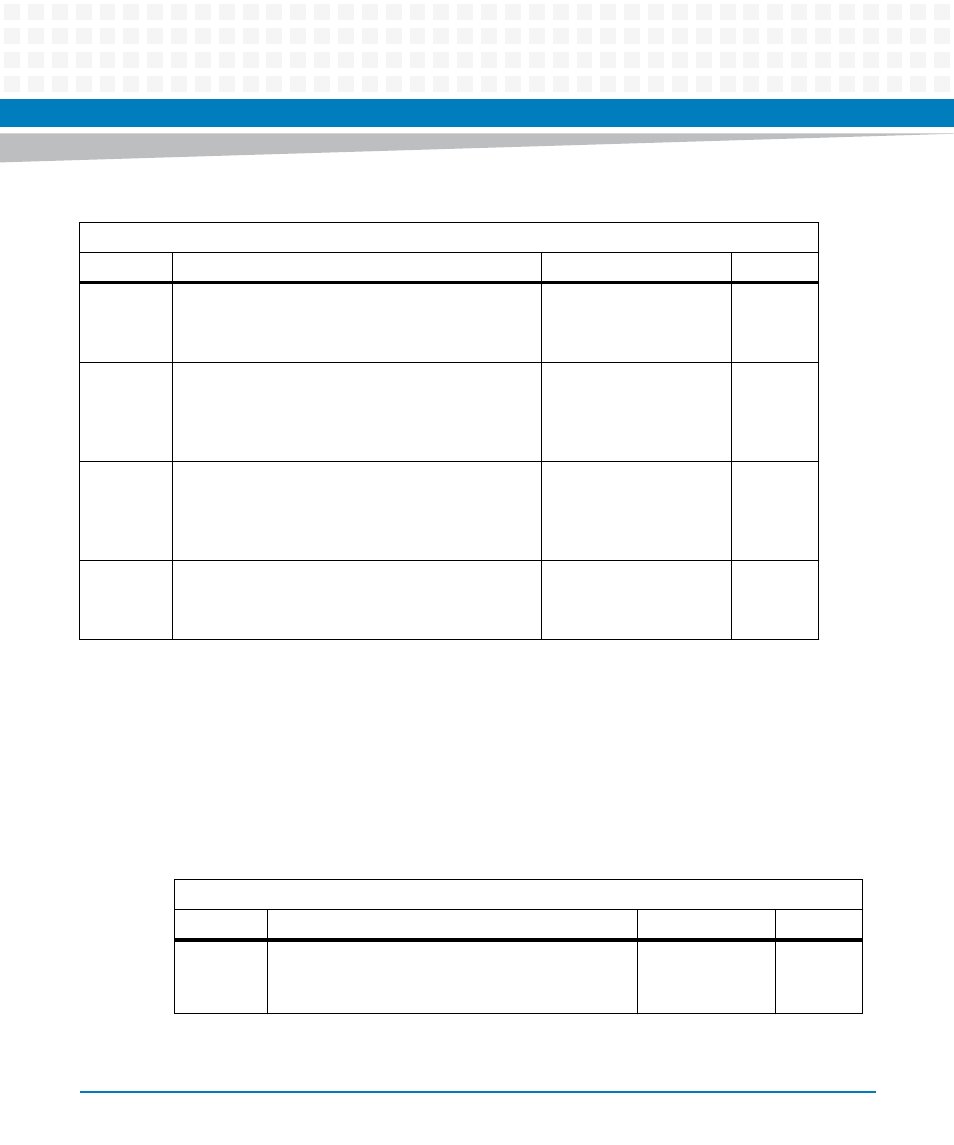

Table 6-64 Flash Status Register (continued)

Address Offset: 0x040

Bit

Description

Default

Access

Table 6-65 Default Boot SPI Flash Write Enable

Address Offset: 0x41

Bit

Description

Default

Access

7:0

Default Boot SPI Flash Write enable/disable.

A write value 0xC3 enables the Boot Block. All other

values disables the Boot Block

-

LPC: w