12 interrupt control and status registers, 1 rtm interrupt status register, 2 external interrupt status register – Artesyn ATCA-7365 Installation and Use (May 2014) User Manual

Page 205: Table 6-58, Rtm spi read register, Table 6-59, External interrupt status register, Maps and registers

Maps and Registers

ATCA-7365 Installation and Use (6806800K65M)

205

A write access to the RTM SPI Address/Command Register with the Command Bit 1 (Read)

starts a SPI read transaction. The value of the RTM SPI Read Register contains the data read

from the SPI device.

6.4.12 Interrupt Control and Status Registers

The interrupt status registers indicate the status of the interrupt input signals. They are read

only registers. When an interrupt is active the corresponding status bit is read 1. Write access

to these register bits does not have any impact.

6.4.12.1 RTM Interrupt Status Register

The RTM Interrupt Status Register will be located in the RTM SPI address space. The host can

access the RTM register using the RTM SPI Master Interface.

No RTM interrupt sources are defined yet.

6.4.12.2 External Interrupt Status Register

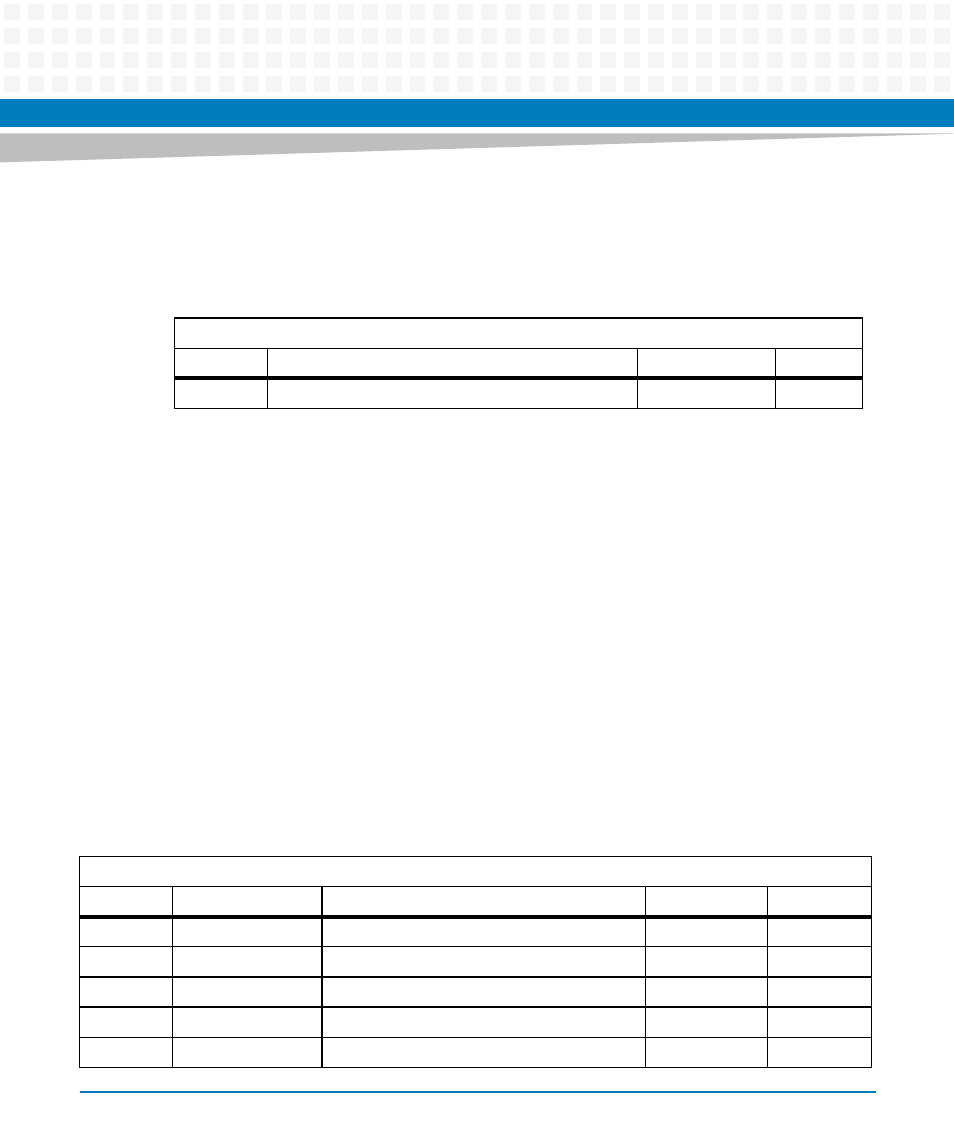

Table 6-58 RTM SPI Read Register

Address Offset: 0x19

Bit

Description

Default

Access

7:0

RTM SPI read data

-

LPC: r

Table 6-59 External Interrupt Status Register

Address Offset: 0x20

Bit

Signal

1

Description

Default

Access

0

IPMC2HOST_INT_

IPMC signals interrupt

Ext.

LPC: r

1

LM75_INT_

Interrupt input from payload Temp sensor

Ext.

LPC: r

2

SFMEM_IRQ_

Interrupt from SFMEM Module

Ext.

LPC: r

3

THERM_SEN0

IRQ request from 82599 Thermsen0

Ext.

LPC: r

4

THERM_SEN1

IRQ request from 82599 Thermsen1

Ext.

LPC: r