2 spi register decoding, 2 post code register, Table 6-7 – Artesyn ATCA-7365 Installation and Use (May 2014) User Manual

Page 167: Ipmc spi register, Table 6-8, Post code register, Maps and registers

Maps and Registers

ATCA-7365 Installation and Use (6806800K65M)

167

6.3.1.2

SPI Register Decoding

All SPI accesses from the IPMC towards the FPGA with the SPI select signal IPMC_SPI_SS_FPGA_

asserted are accepted.

6.3.2

POST Code Register

The FPGA provides an 8 bit wide register to store POST codes to the LPC I/O address 0x80. The

two nibbles of the register are converted to 7 segment codes and are displayed as two hex

values by two 7 segment LED Displays.

The IPMC may read the POST code using the SPI interface (with the signal IPMC_SPI_SS_FPGA_

asserted) and the SPI address 0x7F.

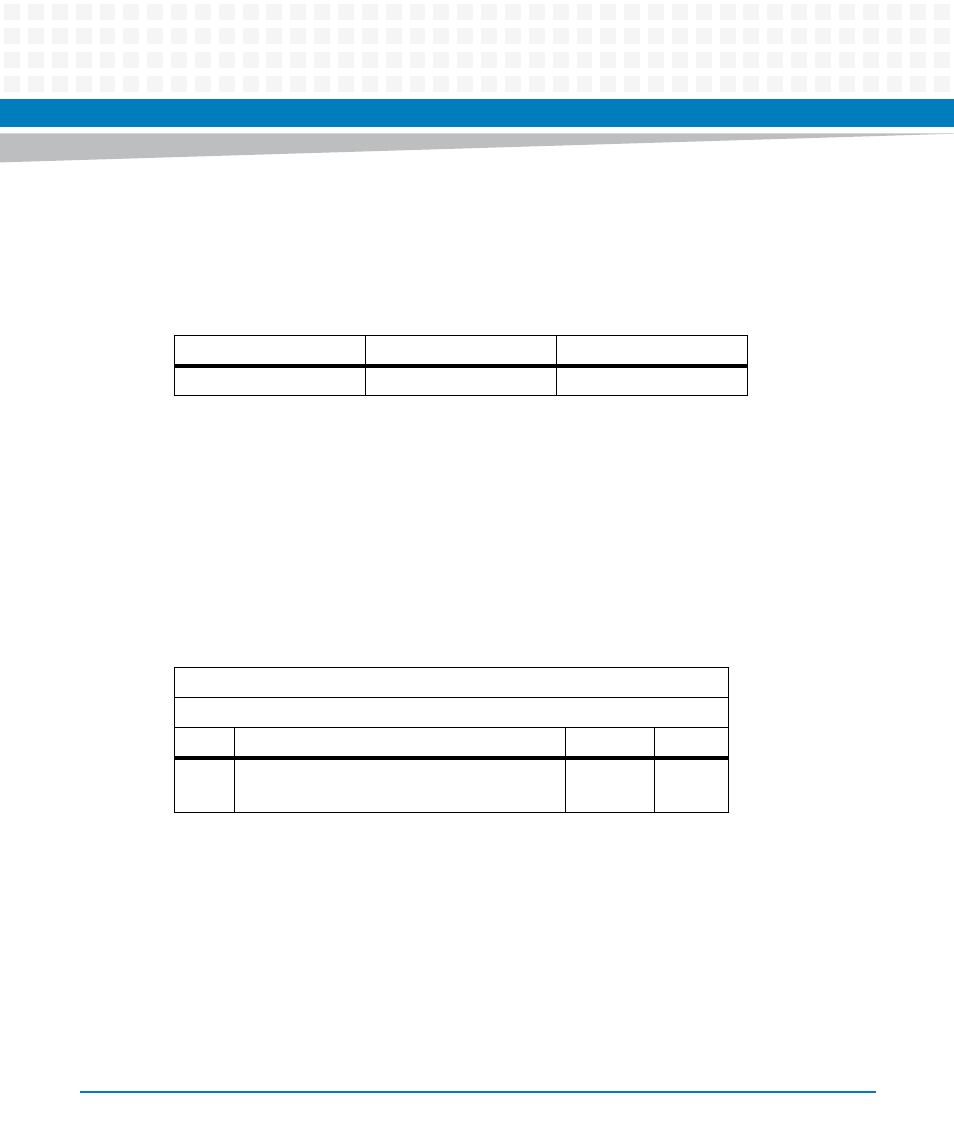

Table 6-7 IPMC SPI Register

SPI Address Range

Address Range Name

Description

0x00 – 0x7F

REGISTERS

FPGA Registers

Table 6-8 POST Code Register

LPC I/O Address: 0x80

IPMC SPI Address: 0x7f

Bit

Description

Default

Access

7:0

POST codes from host

0

LPC: r/w

IPMC: r