4 uart1 and uart2 register map, 1 uart register overview, Table 6-23 – Artesyn ATCA-7365 Installation and Use (May 2014) User Manual

Page 175: Logical device 0x74 reserved register, Table 6-24, Logical device 0x75 reserved register, Table 6-25, Logical device 0xf0 reserved register, Maps and registers

Maps and Registers

ATCA-7365 Installation and Use (6806800K65M)

175

6.3.4

UART1 and UART2 Register Map

The LPC IO Base addresses BASE1 for UART1 and BASE2 for UART2 are set up during Super IO

configuration. See

Super IO Configuration Registers

6.3.4.1

UART Register Overview

shows the registers and their addresses as offsets of a base address for

one of the two UARTs.

An Interrupt is activated by enabling this device (offset 0x30), setting this register to a non-

zero value and setting any combination of bits 0-4 in the corresponding UART IER and the

occurrence of the corresponding UART event (i.e. Modem Status Change, Receiver Line Error

Condition, Transmit Data Request, Receiver Data Available or Receiver Time Out) and setting

the OUT2 bit in the MCR.

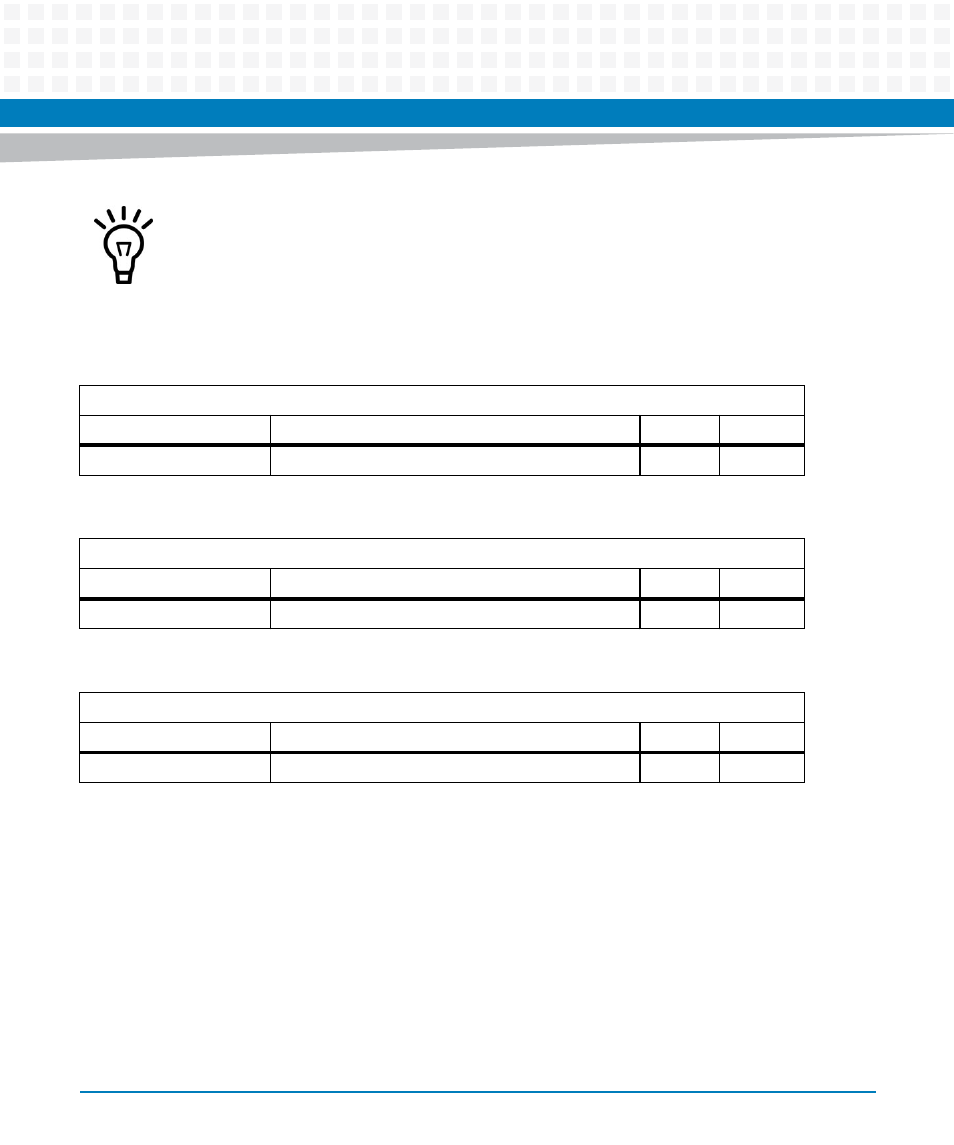

Table 6-23 Logical Device 0x74 Reserved Register

Index Address: 0x74

Bit

Description

Default

Access

7:0

Reserved

0x04

LPC: r

Table 6-24 Logical Device 0x75 Reserved Register

Index Address: 0x75

Bit

Description

Default

Access

7:0

Reserved

0x04

LPC: r

Table 6-25 Logical Device 0xF0 Reserved Register

Index Address: 0xF0

Bit

Description

Default

Access

7:0

Reserved

0x04

LPC: r