9 spd prom mux control register, Table 6-47, Spd prom mux control registerr – Artesyn ATCA-7365 Installation and Use (May 2014) User Manual

Page 196: Maps and registers

Maps and Registers

ATCA-7365 Installation and Use (6806800K65M)

196

6.4.9

SPD PROM MUX Control Register

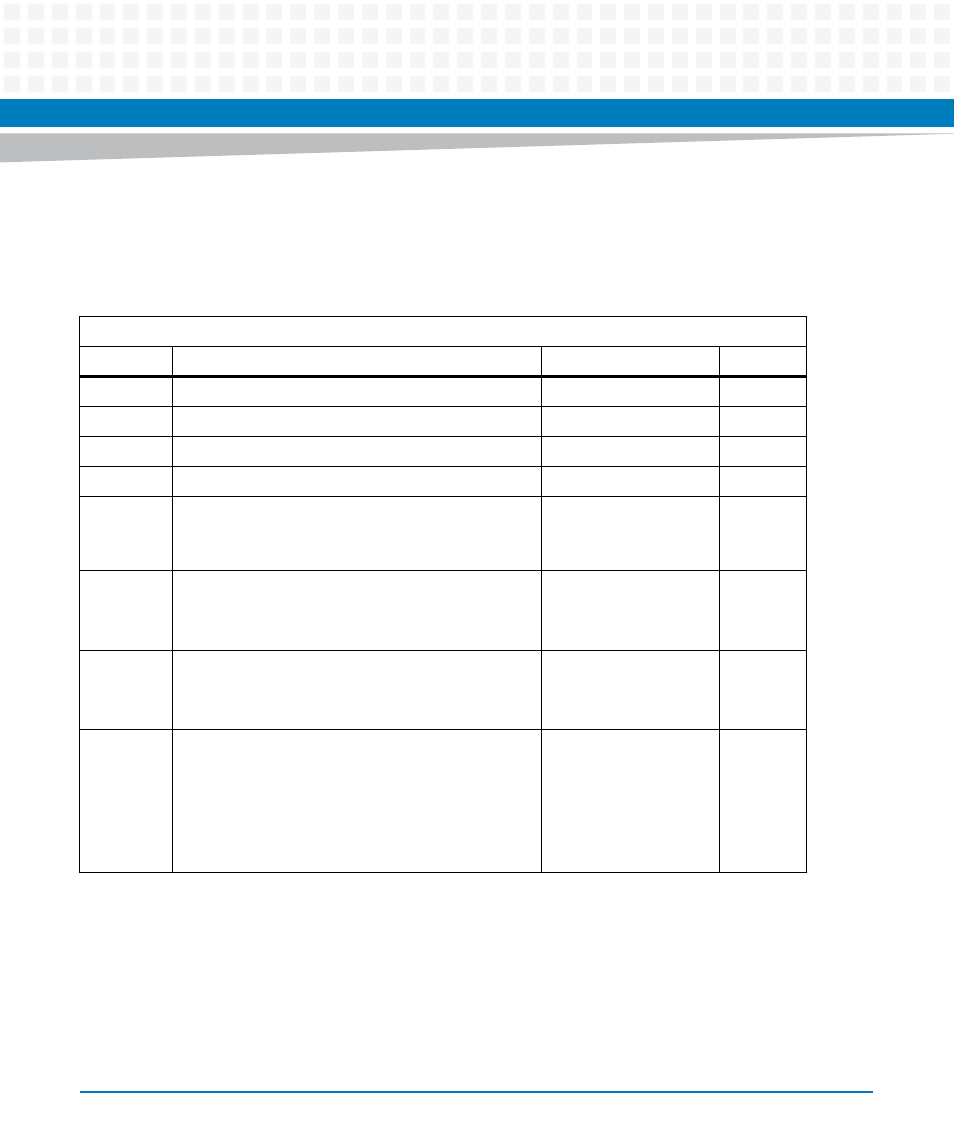

Table 6-47 SPD PROM MUX Control Registerr

Address Offset: 0x08

Bit

Description

Default

Access

0

Signal Level of SMBUS_MUX0_IN

Ext.

r

1

Signal Level of SMBUS_MUX1_IN

Ext.

r

2

Signal Level of BIOS_POST_CMPLT_IN

Ext.

r

3

Reserved

0

r

4

SMBUS_MUX0_OUT.

1

0: SMBUS_MUX0_OUT is driven low

1: SMBUS_MUX0_OUT is driven high

Ext.:

SMBUS_MUX0_IN

LPC: r

IPMC: r/w

5

SMBUS_MUX1_OUT.

2

0: SMBUS_MUX1_OUT is driven low

1: SMBUS_MUX1_OUT is driven high

Ext.:

SMBUS_MUX1_IN

LPC: r

IPMC: r/w

6

BIOS_POST_CMPLT_OUT.

3

0: BIOS_POST_CMPLT_IN is driven low

1: BIOS_POST_CMPLT_IN is driven high

Ext.:

BIOS_POST_CMPLT_IN

LPC: r

IPMC: r/w

7

SPD PROM MUX locked by BIOS

1: The output signals XXX_OUT are directly

controlled by the corresponding input signals

XXX_IN.

0: The output signals XXX_OUT are controlled by the

corresponding bits 4 to 6.

0

LPC: r/w

IPMC: r

1. When the SPD PROM MUX is locked by BIOS (Bit 7 is set) the signal level of SMBUS_MUX0_IN is read.Write transactions

are ignored.

2. When the SPD PROM MUX is locked by BIOS (Bit 7 is set) the signal level of SMBUS_MUX1_IN is read. Write transactions

are ignored.

3. When the SPD PROM MUX is locked by BIOS (Bit 7 is set) the signal level of BIOS_POST_CMPLT_IN is read. Write

transactions are ignored.