17 miscellaneous status and control register, 18 debug switch and led status register, Table 6-70 – Artesyn ATCA 7370 / ATCA 7370-S Installation and Use (June 2014) User Manual

Page 171: Miscellaneous status and control register, Table 6-71, Debug switch and led status register, Maps and registers

Maps and Registers

ATCA-7370/ATCA-7370-S Installation and Use (6806800P54F)

171

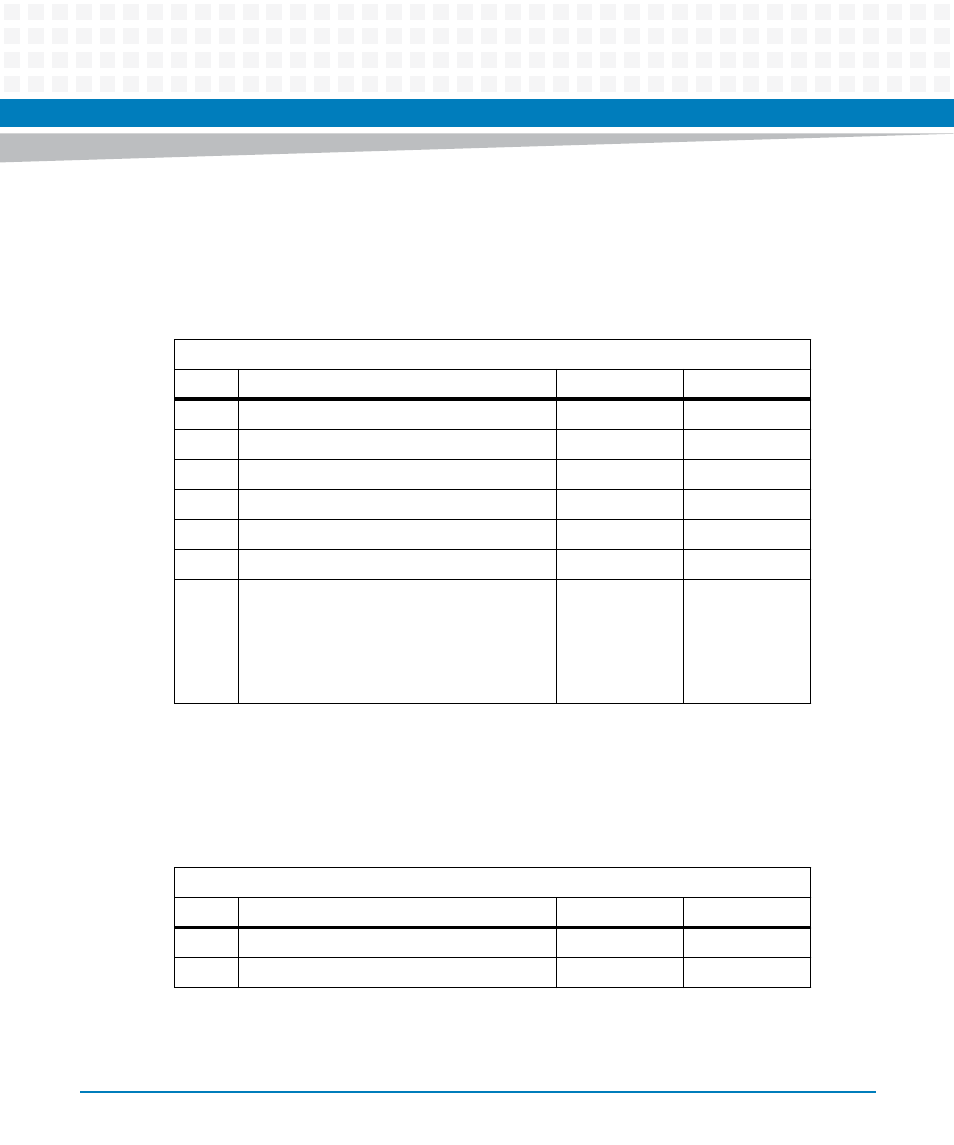

6.3.17 Miscellaneous Status and Control Register

The Miscellaneous register provides the status of hardware signals for IPMC to monitor, like the

occupation status of both CPU sockets

6.3.18 Debug Switch and LED Status Register

Table 6-70 Miscellaneous Status and Control Register

Address Offset: 0x58

Bit

Description

Default

Access

0

FRB_HDL_SW_N

Ext.

r

1

BMC_WDO_N

Ext.

r

3:2

CPU_SKTOCC_N[1:0]

Ext.

r

4

CPU_IVY_N

Ext.

r

5

PCH_HOT_N

Ext.

r

6

Reserved

0

r

7

IPMC to payload NMI request:

1: NMI active

0: NMI inactive

Note: FPGA_PCH GPIO3 signal will also be

controlled by warm-reset procedure

0

IPMC: r/w

LPC: r

Table 6-71 Debug Switch and LED Status Register

Address Offset: 0x59

Bit

Description

Default

Access

3:0

DBG_SW[3:0]

Ext.

r

7:4

FPGA_DBG_LED_N[3:0]

Ext.

r