2 ipmc spi register map, Table 6-42, Fpga register map overview – Artesyn ATCA 7370 / ATCA 7370-S Installation and Use (June 2014) User Manual

Page 151: Maps and registers

Maps and Registers

ATCA-7370/ATCA-7370-S Installation and Use (6806800P54F)

151

6.3.2

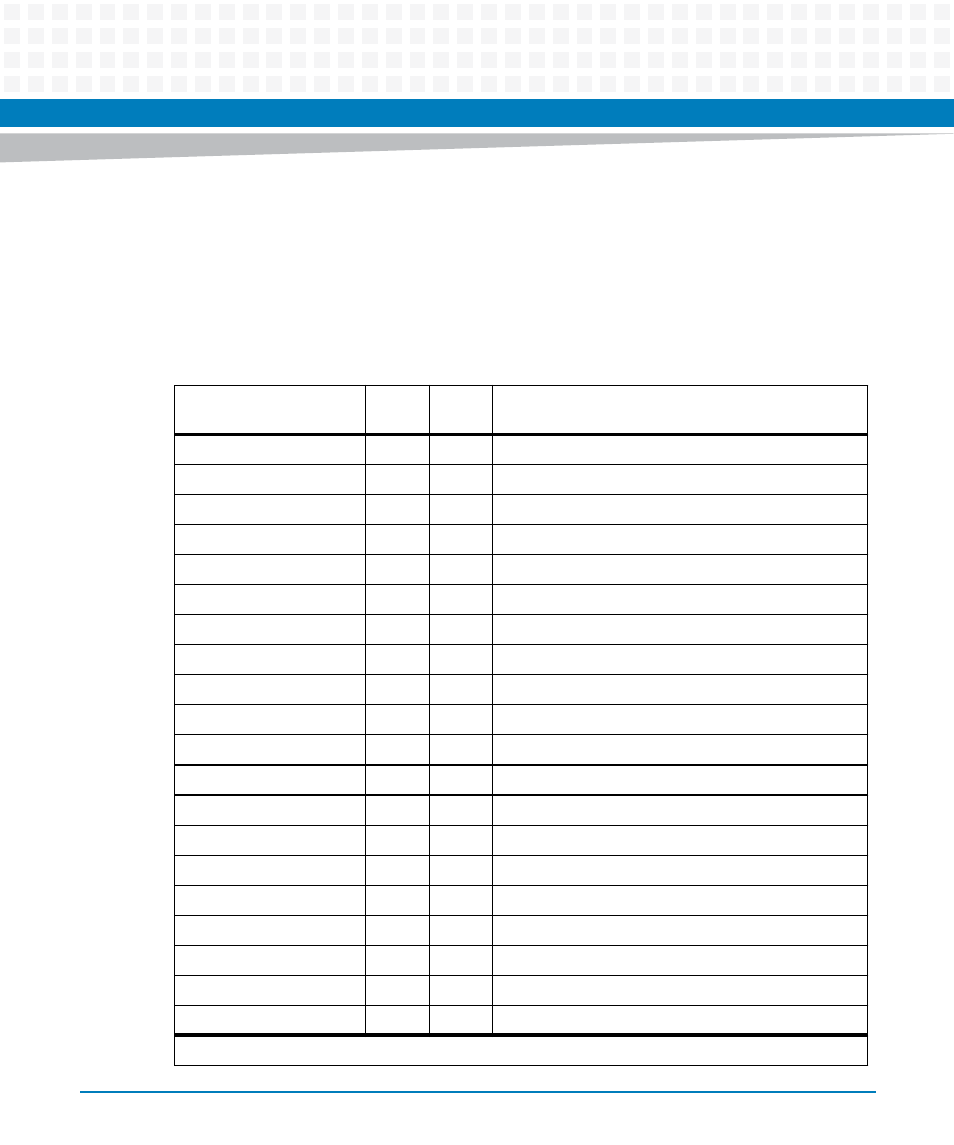

IPMC SPI Register Map

The FPGA registers may be accessed using the IPMC SPI transactions (with the signal

BMC_SPI_S0_N asserted). See

Table 6-42 "FPGA Register Map Overview"

. A SPI write-access to

an address not listed in this table or marked with a "-" in the IPMC SPI column is ignored. A

corresponding read access delivers always zero.

Table 6-42 FPGA Register Map Overview

Address Offset

1

LPC

I/O

IPMC

SPI

Description

0x00

r

r

Module Identification Register

0x01

r

r

FPGA Version Register

0x02

-

-

Reserved

0x03

rw

r

Serial Redirection Control Register

0x04

r

rw

Serial over LAN (SOL) Control Register

0x05

r

rw

Serial Routing Register

0x06

r

rw

IPMC Power Level Register

0x07

-

rw

Payload Power Control Register

0x08

rw

rw

I2C Switch Control Register

0x09

-

rw

Payload Power-button Register

0x0A~0E

-

-

Reserved

0x0F

rw

rw

Reset Mask Register

0x10

rw

rw

Reset Function Register

0x11

-

w

IPMC Reset Payload Request Register

0x12

w

-

BIOS Reset Payload Request Register

0x13

w

-

OS Reset Payload Request Register

0x14

-

rw

Payload Reset Source for IPMC Register

0x15

rw

-

Payload Reset Source for BIOS Register

0x16

rw

-

Payload Reset Source for OS Register

0x17

-

rw

IPMC Watchdog Timeout Register

1

For LPC I/O access, add the LPC I/O Base Address 0x600