13 flash control register, 14 rtm status and control register, Table 6-66 – Artesyn ATCA 7370 / ATCA 7370-S Installation and Use (June 2014) User Manual

Page 168: Flash control register, Table 6-67, Rtm status and control register, Maps and registers

Maps and Registers

ATCA-7370/ATCA-7370-S Installation and Use (6806800P54F)

168

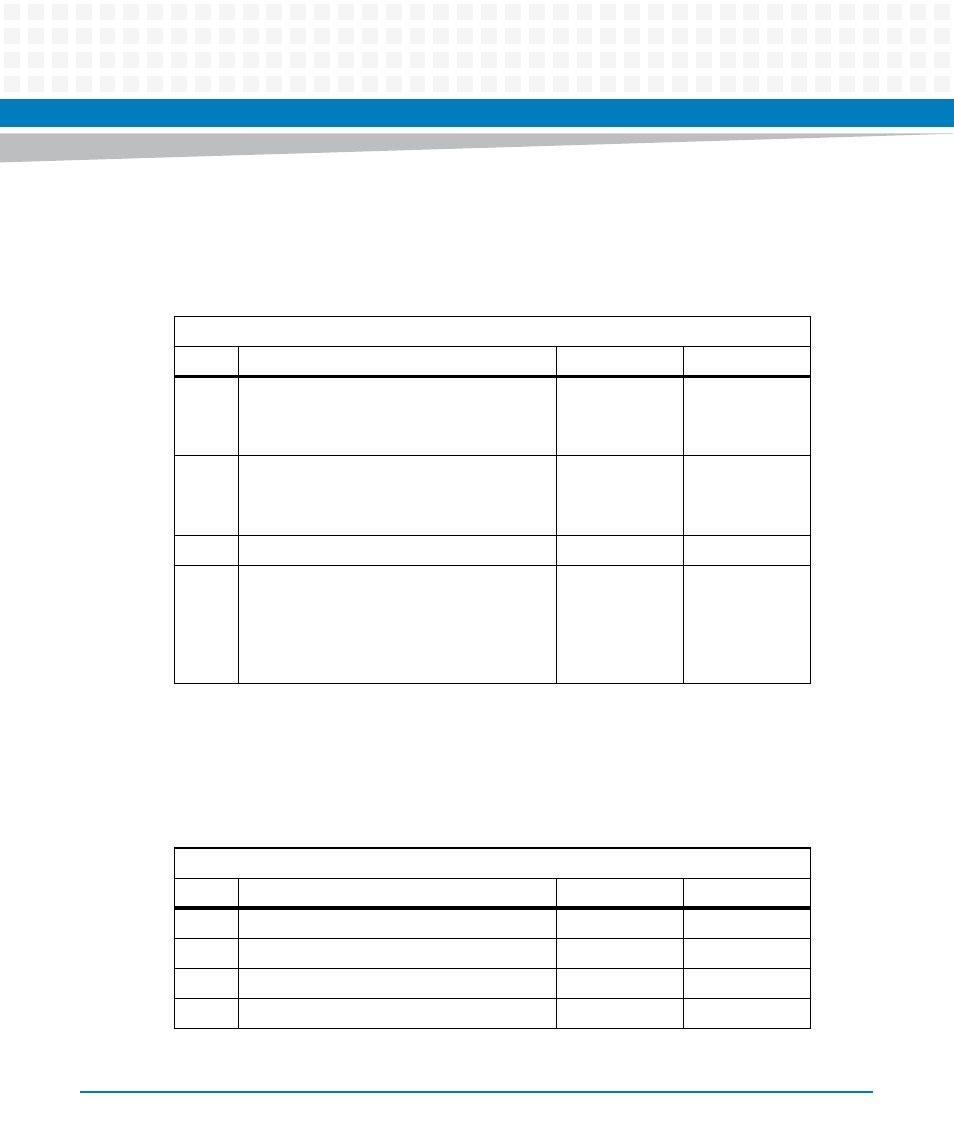

6.3.13 Flash Control Register

6.3.14 RTM Status and Control Register

Table 6-66 Flash Control Register

Address Offset: 0x40

Bit

Description

Default

Access

0

Inverted of DEF_SPI_WP_N output

0: DEF_SPI_WP_N output high

1: DEF_SPI_WP_N output low

0

LPC: r

IPMC:r/w

1

Inverted of REC_SPI_WP_N output

0: REC_SPI_WP_N output high

1: REC_SPI_WP_N output low

0

LPC: r

IPMC:r/w

6:2

Reserved

00000

r

7

Payload Boot SPI Flash select.

0: Default Boot Flash linked to PCH, Recovery

one to IPMC

1: Recovery Boot Flash linked to PCH, Default

one to IPMC

0

LPC: r

IPMC:r/w

Table 6-67 RTM Status and Control Register

Address Offset: 0x4A

Bit

Description

Default

Access

0

RTM_PS1_N

Ext.

r

1

RTM_ALL_PG

Ext.

r

2

RTM_MP_PG

Ext.

r

3

RTM_PP_PG

Ext.

r