Table 6-33, Interrupt identification register decode, Maps and registers – Artesyn ATCA 7370 / ATCA 7370-S Installation and Use (June 2014) User Manual

Page 137

Maps and Registers

ATCA-7370/ATCA-7370-S Installation and Use (6806800P54F)

137

5:4

Reserved

0

LPC: r

7:6

FIFO Mode Enable bits:

00: Default mode

01: Reserved

10: Reserved

11: FIFO mode

0

LPC: r

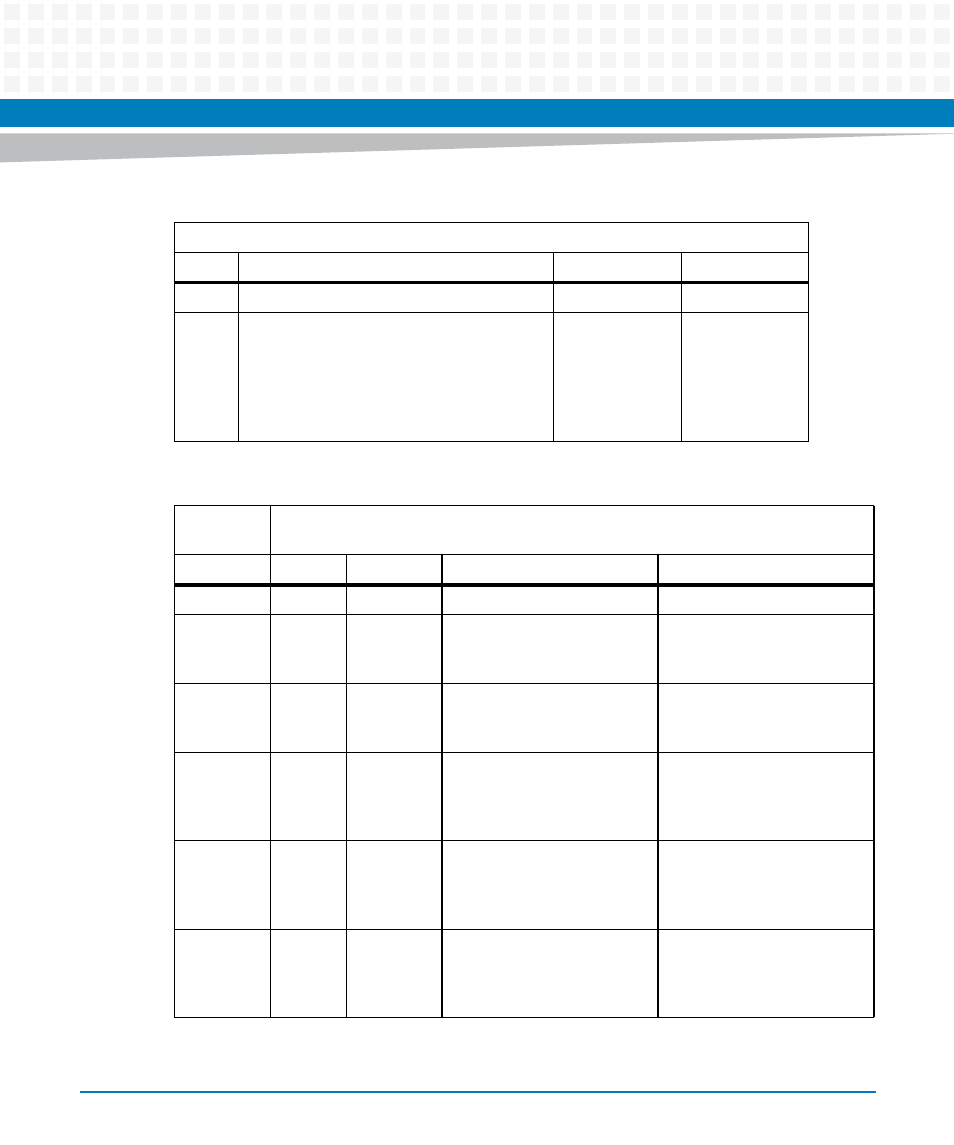

Table 6-33 Interrupt Identification Register Decode

Interrupt

ID

Interrupt Set/Reset Function

3:0

Priority

Type

Source

Reset Control

0b0001

-

None

No Interrupt is pending

-

0b0110

1

Receiver

Line Status

Overrun Error, Parity Error,

Framing Error, Break

Interrupt.

Reading the Line Status

Register.

0b0100

2

Received

Data

Available.

Non-FIFO mode: Receive

Buffer is full.

Non-FIFO mode: Reading the

Receiver Buffer Register.

FIFO mode: Trigger level was

reached.

FIFO mode: Reading bytes

until Receiver FIFO drops

below trigger level or setting

RESETRF bit in FCR register.

0b1100

Character

Timeout

indication.

FIFO Mode only: At least 1

character is in receiver FIFO

and there was no activity for a

time period.

Reading the Receiver FIFO or

setting RESETRF bit in FCR

register

0b0010

3

Transmit

FIFO Data

Request

Non-FIFO mode: Transmit

Holding Register Empty

Reading the IIR Register (if

the source of the interrupt) or

writing into the Transmit

Holding Register.

Table 6-32 Interrupt Identification Register (IIIR)

LPC IO Address: Base + 2

Bit

Description

Default

Access