General connectors, Jtag connector (j9), General connectors –50 – Altera Cyclone II DSP Development Board User Manual

Page 58

2–50

Reference Manual

Altera Corporation

Cyclone II DSP Development Board

August 2006

General Connectors

General

Connectors

This section describes the general connectors on the Cyclone II DSP

development board.

JTAG Connector (J9)

The Cyclone II DSP development board contains one JTAG connector (J9).

This connector provides communication between a PC running the

Quartus II software and the Cyclone II DSP development board. The pins

on J9 are connected to J12 through 0-

Ω series resistors, and care must be

taken so that signal contention does not occur between the two

connectors.

The EP2C70 can be programmed with the JTAG interface. A JTAG UART

megafunction is also provided on the Nios

®

II Embedded Processor

Evaluation Edition, version 6.0.1 CD-ROM for designers to instantiate in

their design as well as a host-side (PC-side) API for transferring data

using scripts or compiled programs. You can reach speeds up to 1 Mbps.

Nios or Nios II based programmable logic device (PLD) designs can use

this interface to control and/or download code.

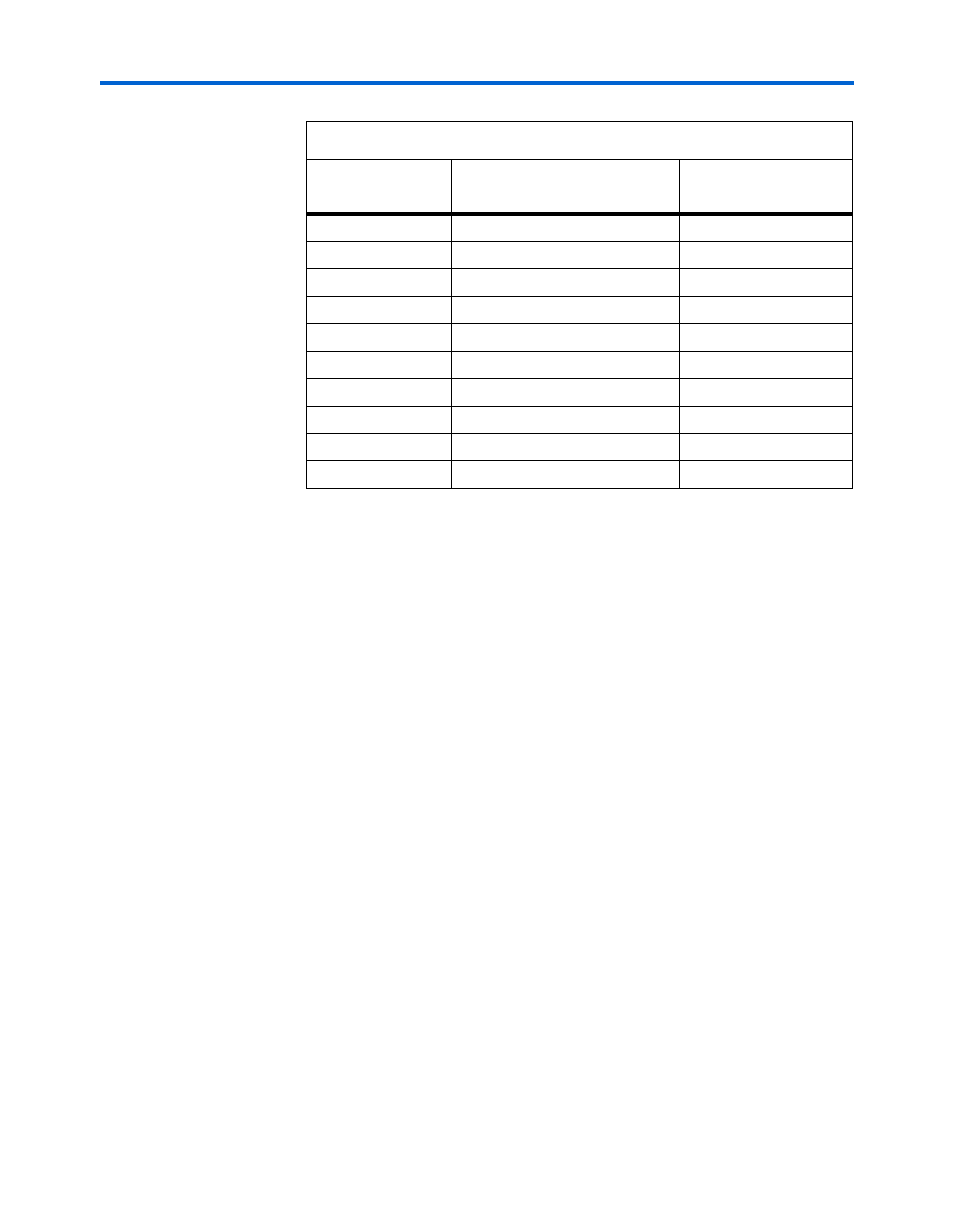

EVM_FSX0

U34.23

G22

EVM_IACK

U34.54

N26

EVM_INT0

U34.53

M22

EVM_INT1

U34.48

M25

EVM_INT2

U34.67

AC26

EVM_INT3

U34.68

L23

EVM_INUM0

U34.58

P1

EVM_OEN

U40.75

AA23

EVM_RESET

U34.59

P25

EVM_STAT0

U34.66

L20

Table 2–25. TI-EVM Connector Pin-Outs (Part 4 of 4)

Schematic Signal

Name

TI-EVM Connector (U34, U40)

Pin Number

Cyclone II (U12) Pin

Number