Device capabilities, Error reporting – Altera V-Series Avalon-MM DMA User Manual

Page 28

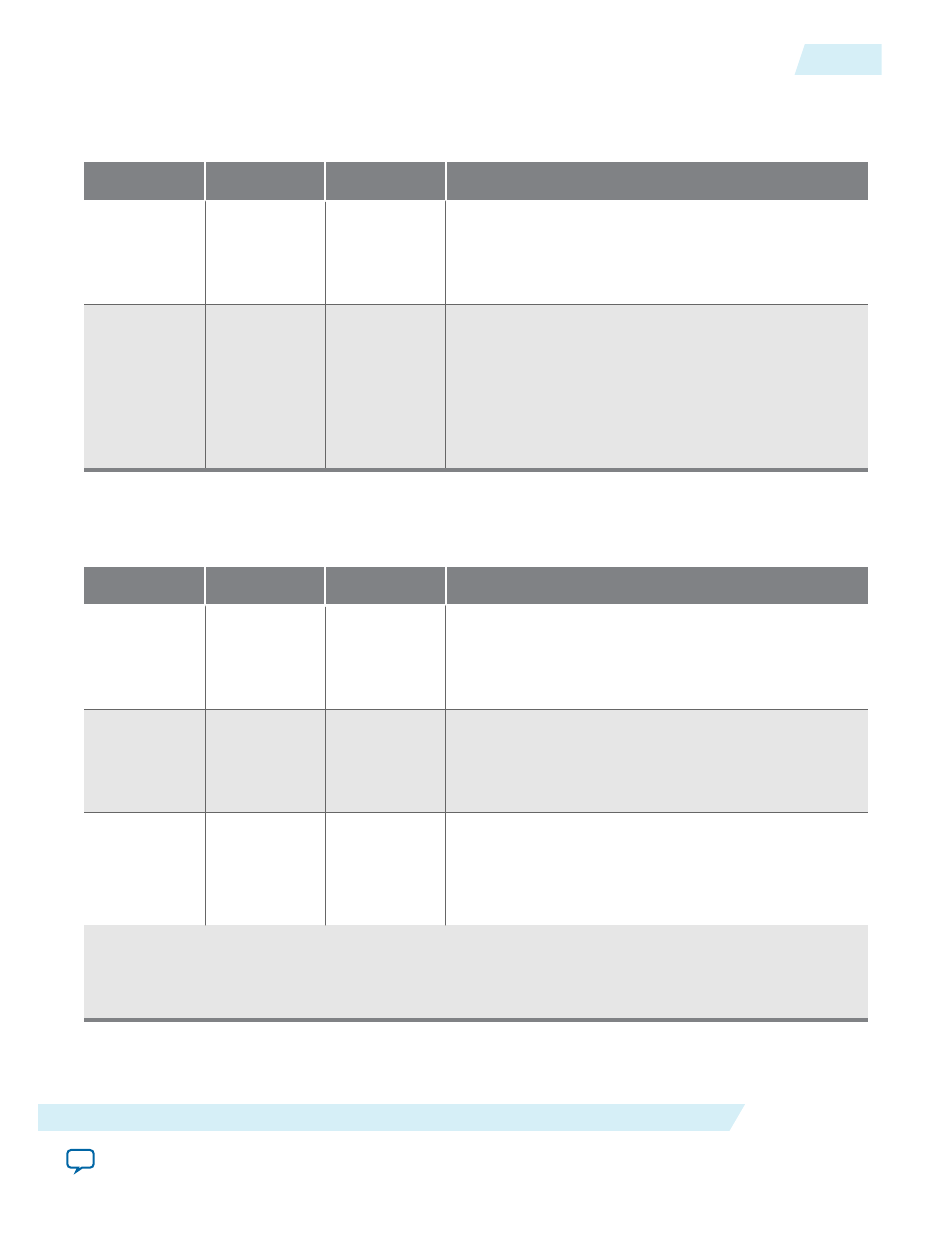

Device Capabilities

Table 3-4: Capabilities Registers

Parameter

Possible Values

Default Value

Description

Maximum

payload size

128 bytes

256 bytes

128 bytes

Specifies the maximum payload size supported. This

parameter sets the read-only value of the max payload

size supported field of the Device Capabilities register

(0x084[2:0]). Address: 0x084.

Implement

completion

timeout

disable

On/Off

On

For Endpoints using PCI Express version 2.1 or 3.0, this

option must be On. The timeout range is selectable.

When On, the core supports the completion timeout

disable mechanism via the PCI Express

Device

Control Register 2

. The Application Layer logic must

implement the actual completion timeout mechanism

for the required ranges.

Error Reporting

Table 3-5: Error Reporting

Parameter

Value

Default Value

Description

Advanced

error

reporting

(AER)

On/Off

Off

When On, enables the Advanced Error Reporting (AER)

capability.

ECRC

checking

On/Off

Off

When On, enables ECRC checking. Sets the read-only

value of the ECRC check capable bit in the

Advanced

Error Capabilities and Control Register

. This

parameter requires you to enable the AER capability.

ECRC

generation

On/Off

Off

When On, enables ECRC generation capability. Sets the

read-only value of the ECRC generation capable bit in

the

Advanced Error Capabilities and Control

Register

. This parameter requires you to enable the

AER capability.

Note:

1. Throughout this user guide, the terms word, dword and qword have the same meaning that they have

in the PCI Express Base Specification. A word is 16 bits, a dword is 32 bits, and a qword is 64 bits.

Related Information

UG-01154

2014.12.18

Device Capabilities

3-7

Parameter Settings

Altera Corporation