Teledyne LeCroy WavePro Automation Command User Manual

Page 226

Automation Command and Query Reference Manual - Control Reference

PLLFrequency

Double

From 2488 to 2.488e+008 step 1

Range

This setting controls the bandwidth of a single-pole PLL emulation that can be selectd as PLL Type

"FC Golden". This bandwidth is usuall controlled by app.SDA2.CDR.CutOffDivisor, and the resulting

bandwidth can then be read from this control variable. When app.SDA2.CDR.PLLFrequency is set,

the CutOffDivisor is set based on this value and on the current SignalFrequency. Please see

CutOffDivisor for further explanation.

Description

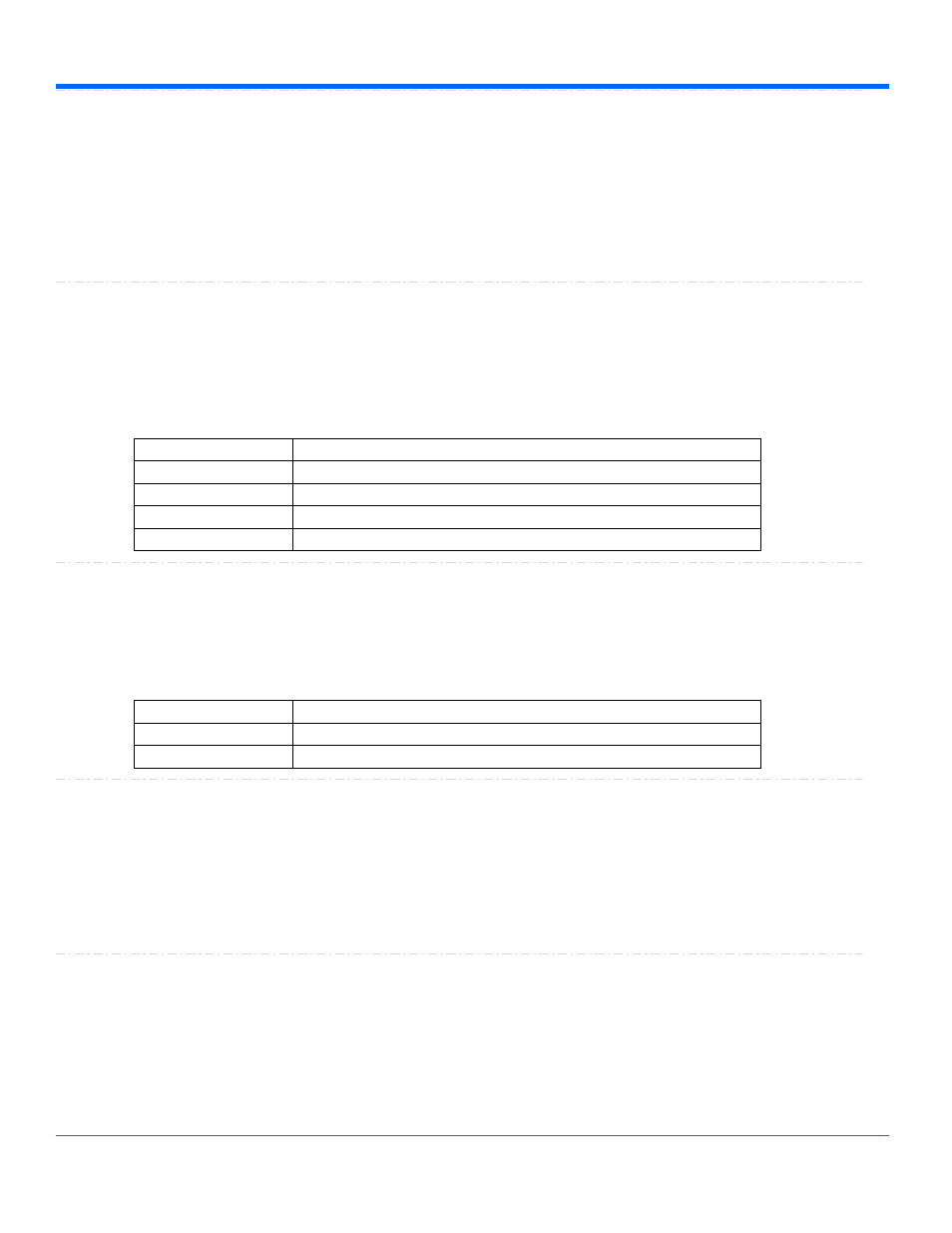

PLLType

Enum

Sets the type of our software PLL emulation. Within SDA2 user interface other types besides those

shown below may be listed, if so they are mapped onto Custom, they select Custom PLL with

appropriate settings.

Description

Values

Custom

1 pole (and 1 parasitic 0) or 2 pole PLL, with customizable settings

DVI

Reuses the Custom 1 pole, pole at 4MHz, zero at 70MHz (that is, negligible).

FBDIMM

Two 2 pole PLLs separated by a Tranport Delay, preset to values needed for FB-DIMM.

GOLDEN

1 pole PLL, when CutOffDivisor is at its default value of 1667 this it the Fibre Channel golden PLL

PCIEXPRESS

PCI-Express Gen 1 preset. SDA2 adds three PCIe Gen2 PLLs, as specified in the PCIE CEM spec.

RefClkSlope

Enum

When UseRefClk is set to ON, then this control specifies which edges of the reference clock signal

should be used to sample the data signal.

Description

Values

Both

Use both edges - half frequency clock

Neg

Use negative going edges

Pos

Use positive going edges

SignalFrequency

Double

From 90000 to 4e+010 step 1

Range

if UseRefClk is OFF, then SignalFrequency is the BaseFrequency, which is derived from the data

signal by FindBaseFrequency. If UseRefClk is ON, then SignalFrequency is BaseFrequency

multiplied by ClockMultiplier; BaseFrequency is derived from the reference clock signal by

FindBaseFrequency.

Description

UsePLL

Bool

The expected use of SDA2 is with UsePLL set to true. In that state, the SDA2 uses the selected PLL

type to produce a clock signal that tracks variations in the data rate. Variations at frequencies low

enough for the PLL to track effectively are not counted as jitter. If the data is produced using a very

stable clock, it is possible to set UsePLL to false, in which case the SignalFrequency is uses as a

perfectly stable (mathematically generated) reference; in this state any variation even at very low

frequencies will be seen in jitter measurements.

Description

1-212

918501 RevA