Bit %r,%r, Bit %r,imm4 – Epson S1C63000 User Manual

Page 84

78

EPSON

S1C63000 CORE CPU MANUAL

CHAPTER 4: INSTRUCTION SET

BIT %r,%r’

Test bit of r reg. with r’ reg.

1 cycle

Function:

r

∧

r’

Performs a logical AND of the content of the r’ register (A or B) and the content of the r register

(A or B) to check the bits of the r register. The Z flag is changed due to the operation result, but

the content of the register is not changed.

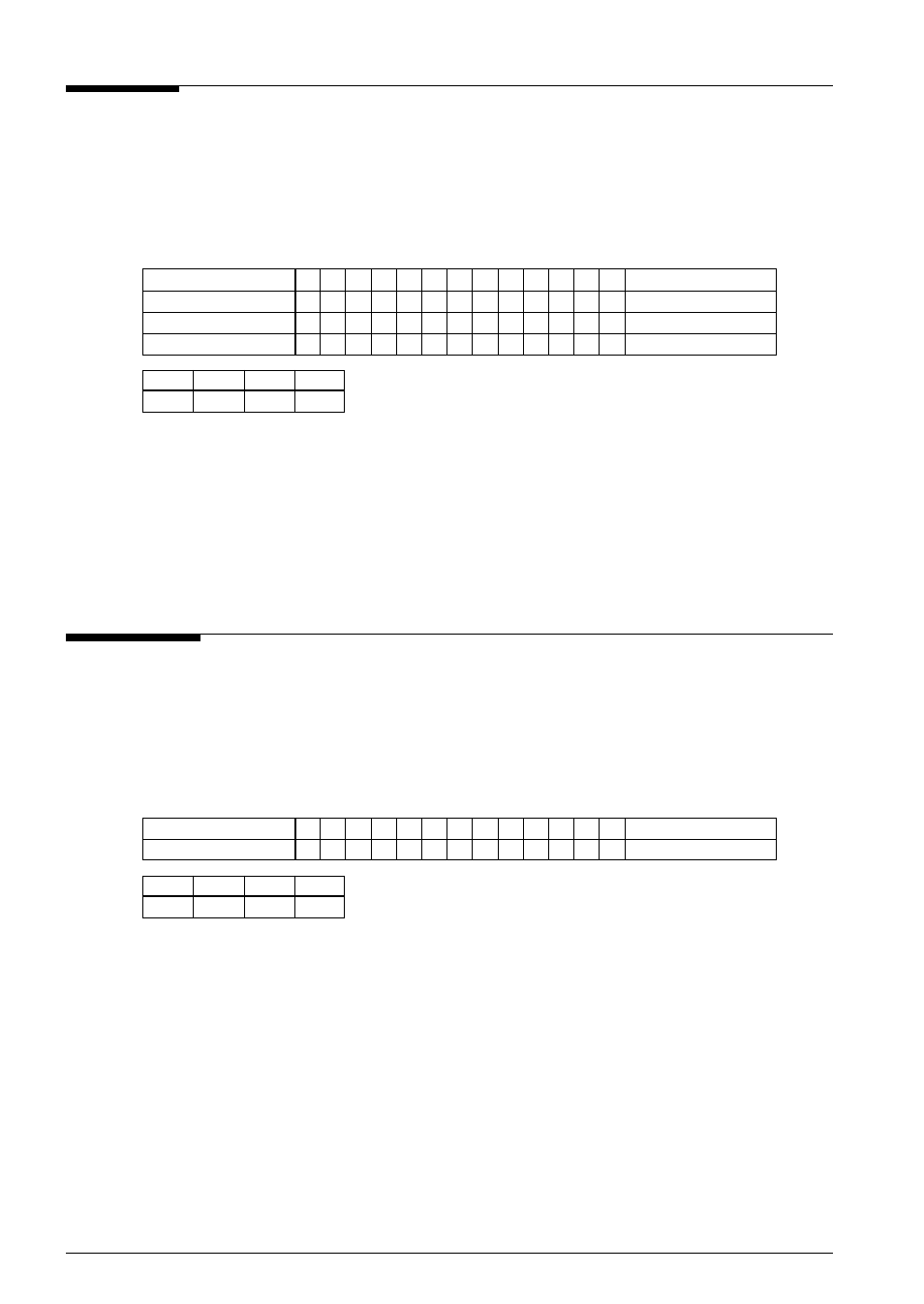

Code:

Mnemonic

MSB

LSB

BIT %A,%A

1

1

0

1

0

1

1

1

1

0

0

0

X

1AF0H, (1AF1H)

BIT %A,%B

1

1

0

1

0

1

1

1

1

0

0

1

X

1AF2H, (1AF3H)

BIT %B,%A

1

1

0

1

0

1

1

1

1

0

1

0

X

1AF4H, (1AF5H)

BIT %B,%B

1

1

0

1

0

1

1

1

1

0

1

1

X

1AF6H, (1AF7H)

Flags:

E

I

C

Z

↓

–

–

↕

Mode:

Src: Register direct

Dst: Register direct

Extended addressing: Invalid

BIT %r,imm4

Test bit of r reg. with immediate data imm4

1 cycle

Function:

r

∧

imm4

Performs a logical AND of the 4-bit immediate data imm4 and the content of the r register (A

or B) to check the bits of the r register. The Z flag is changed due to the operation result, but the

content of the register is not changed.

Code:

Mnemonic

MSB

LSB

BIT %A,imm4

1

1

0

1

0

1

1

0

0 i3 i2 i1 i0

1AC0H–1ACFH

BIT %B,imm4

1

1

0

1

0

1

1

0

1 i3 i2 i1 i0

1AD0H–1ADFH

Flags:

E

I

C

Z

↓

–

–

↕

Mode:

Src: Immediate data

Dst: Register direct

Extended addressing: Invalid