Epson, Chapter 3: cpu operation – Epson S1C63000 User Manual

Page 35

S1C63000 CORE CPU MANUAL

EPSON

29

CHAPTER 3: CPU OPERATION

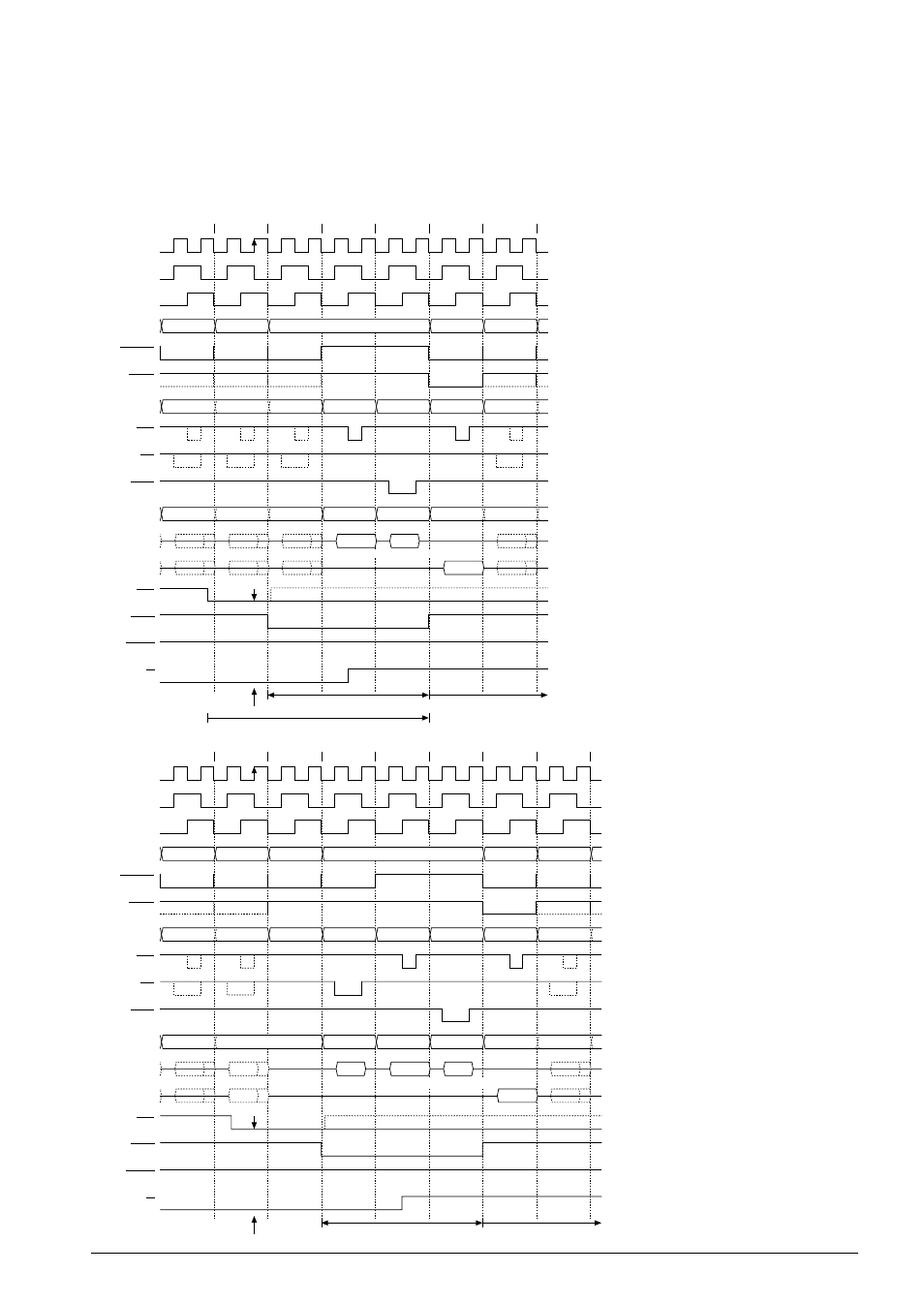

CLK

PK

PL

PC

FETCH

BS16

DBS1/0

WR

RD

RDIV

DA00–DA15

D0–D3

M00–M15

IRQ

IACK

NACK

IF

0

1

2

3

4

5

DUMMY

(010xH)

ANY

pc-3

pc-1

010xH

ANY

2

1

2

ANY

pc

SP2-1

DUMMY

SP1-1

F reg.

xH

pc

ANY

LD %A,[%X]

0

3

ANY

[00xxH]

pc-2

LDB %EXT,imm8

ANY

00xxH

Interrupt processing by the hardware Executing the interrupt service routine

Interrupt sampling

Inte rrupt vector

CLK

PK

PL

PC

FETCH

BS16

DBS1/0

WR

RD

RDIV

DA00–DA15

D0–D3

M00–M15

IRQ

IACK

NACK

IF

0

1

2

3

4

5

ANY

ANY

DUMMY

(010xH)

ANY

pc-2

pc-1

010xH

ANY

ANY

2

1

2

ANY

pc

SP2-1

DUMMY

SP1-1

ANY

F reg.

xH

pc

Interrupt processing by the hardware Executing the interrupt service routine

4–6 cycle

Interrupt sampling

Inte rrupt vector

Fig. 3.5.2.3 Hardware interrupt

(IRQ) sequence

(normal acceptance)

Fig. 3.5.2.4 Hardware interrupt

(IRQ) sequence

(interrupt acceptance

after 1 instruction)

In this chart, the dummy fetch

cycle starts after fetching the

"LD %A, [%X]" instruction

that follows the "LDB %EXT,

imm8" instruction.