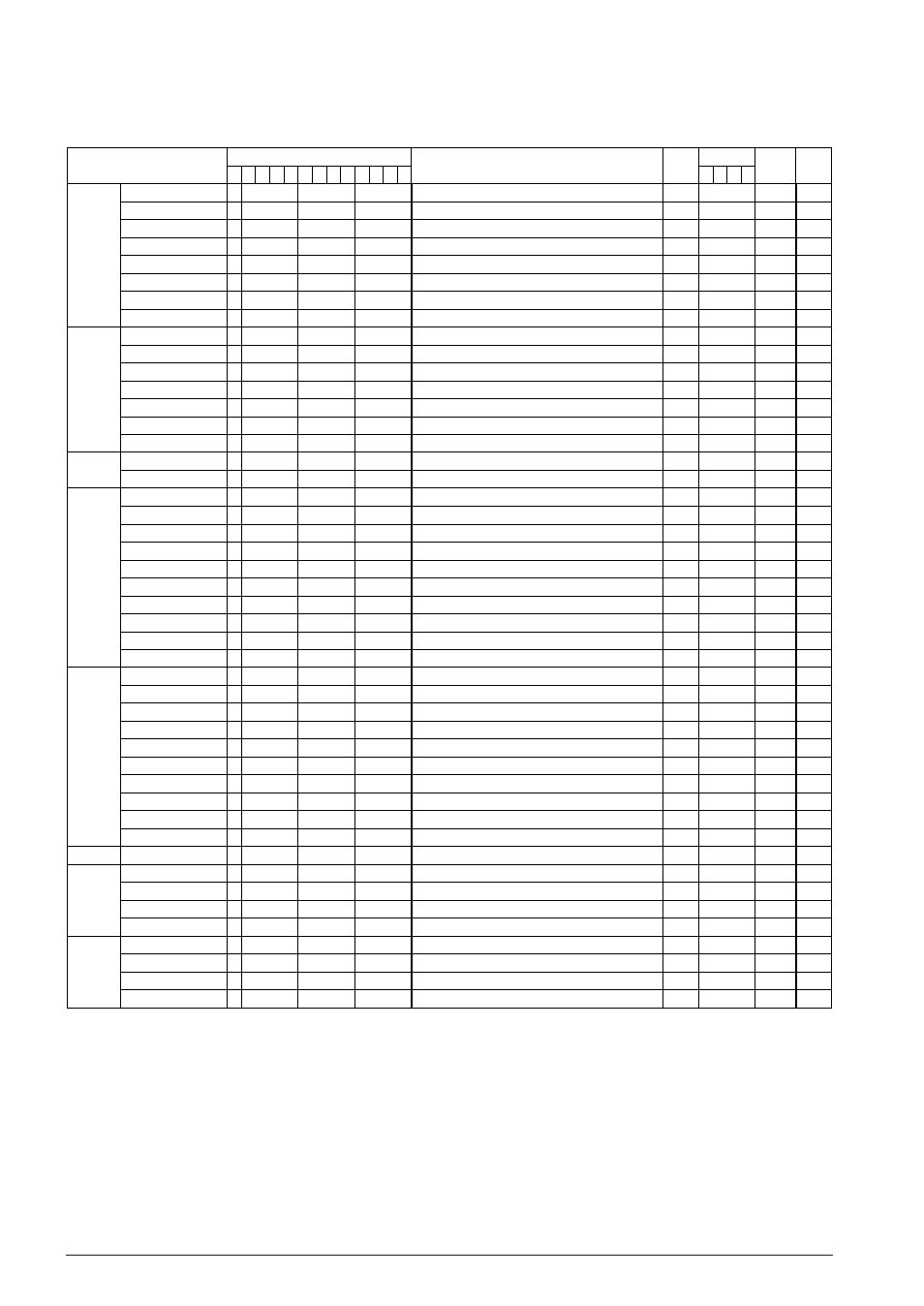

3 instruction list by function, Bit data transfer – Epson S1C63000 User Manual

Page 46

40

EPSON

S1C63000 CORE CPU MANUAL

CHAPTER 4: INSTRUCTION SET

4.2.3 Instruction list by function

LD

%A,%A

%A,%B

%A,%F

%A,imm4

%A,[%X]

%A,[%X]+

%A,[%Y]

%A,[%Y]+

LD

%B,%A

%B,%B

%B,imm4

%B,[%X]

%B,[%X]+

%B,[%Y]

%B,[%Y]+

LD

%F,%A

%F,imm4

LD

[%X],%A

[%X],%B

[%X],imm4

[%X],[%Y]

[%X],[%Y]+

[%X]+,%A

[%X]+,%B

[%X]+,imm4

[%X]+,[%Y]

[%X]+,[%Y]+

LD

[%Y],%A

[%Y],%B

[%Y],imm4

[%Y],[%X]

[%Y],[%X]+

[%Y]+,%A

[%Y]+,%B

[%Y]+,imm4

[%Y]+,[%X]

[%Y]+,[%X]+

EX

%A,%B

EX

%A,[%X]

%A,[%X]+

%A,[%Y]

%A,[%Y]+

EX

%B,[%X]

%B,[%X]+

%B,[%Y]

%B,[%Y]+

1 1 1 1 0 1 1 1 1 0 0 0 0

1 1 1 1 0 1 1 1 1 0 0 1 0

1 1 1 1 1 1 1 1 1 0 1 1 0

1 1 1 1 0 1 1 0 0 i3 i2 i1 i0

1 1 1 1 0 1 1 1 0 0 0 0 0

1 1 1 1 0 1 1 1 0 0 0 0 1

1 1 1 1 0 1 1 1 0 0 0 1 0

1 1 1 1 0 1 1 1 0 0 0 1 1

1 1 1 1 0 1 1 1 1 0 1 0 0

1 1 1 1 0 1 1 1 1 0 1 1 0

1 1 1 1 0 1 1 0 1 i3 i2 i1 i0

1 1 1 1 0 1 1 1 0 0 1 0 0

1 1 1 1 0 1 1 1 0 0 1 0 1

1 1 1 1 0 1 1 1 0 0 1 1 0

1 1 1 1 0 1 1 1 0 0 1 1 1

1 1 1 1 1 1 1 1 1 0 1 0 1

1 0 0 0 0 1 0 1 1 i3 i2 i1 i0

1 1 1 1 0 1 1 1 0 1 0 0 0

1 1 1 1 0 1 1 1 0 1 1 0 0

1 1 1 1 0 1 0 0 0 i3 i2 i1 i0

1 1 1 1 0 1 1 1 1 1 0 1 0

1 1 1 1 0 1 1 1 1 1 0 1 1

1 1 1 1 0 1 1 1 0 1 0 0 1

1 1 1 1 0 1 1 1 0 1 1 0 1

1 1 1 1 0 1 0 0 1 i3 i2 i1 i0

1 1 1 1 0 1 1 1 1 1 1 1 0

1 1 1 1 0 1 1 1 1 1 1 1 1

1 1 1 1 0 1 1 1 0 1 0 1 0

1 1 1 1 0 1 1 1 0 1 1 1 0

1 1 1 1 0 1 0 1 0 i3 i2 i1 i0

1 1 1 1 0 1 1 1 1 1 0 0 0

1 1 1 1 0 1 1 1 1 1 0 0 1

1 1 1 1 0 1 1 1 0 1 0 1 1

1 1 1 1 0 1 1 1 0 1 1 1 1

1 1 1 1 0 1 0 1 1 i3 i2 i1 i0

1 1 1 1 0 1 1 1 1 1 1 0 0

1 1 1 1 0 1 1 1 1 1 1 0 1

1 1 1 1 1 1 1 1 1 0 1 1 1

1 0 0 0 0 1 1 1 1 1 0 0 0

1 0 0 0 0 1 1 1 1 1 0 0 1

1 0 0 0 0 1 1 1 1 1 0 1 0

1 0 0 0 0 1 1 1 1 1 0 1 1

1 0 0 0 0 1 1 1 1 1 1 0 0

1 0 0 0 0 1 1 1 1 1 1 0 1

1 0 0 0 0 1 1 1 1 1 1 1 0

1 0 0 0 0 1 1 1 1 1 1 1 1

1

↓

– – –

Ч

1

↓

– – –

Ч

1

↓

– – –

Ч

1

↓

– – –

Ч

1

↓

– – –

●

1

↓

– – –

Ч

1

↓

– – –

●

1

↓

– – –

Ч

1

↓

– – –

Ч

1

↓

– – –

Ч

1

↓

– – –

Ч

1

↓

– – –

●

1

↓

– – –

Ч

1

↓

– – –

●

1

↓

– – –

Ч

1

Ч

1

Ч

1

↓

– – –

●

1

↓

– – –

●

1

↓

– – –

●

2

↓

– – –

Ч

2

↓

– – –

Ч

1

↓

– – –

Ч

1

↓

– – –

Ч

1

↓

– – –

Ч

2

↓

– – –

Ч

2

↓

– – –

Ч

1

↓

– – –

●

1

↓

– – –

●

1

↓

– – –

●

2

↓

– – –

Ч

2

↓

– – –

Ч

1

↓

– – –

Ч

1

↓

– – –

Ч

1

↓

– – –

Ч

2

↓

– – –

Ч

2

↓

– – –

Ч

1

↓

– – –

Ч

2

↓

– – –

●

2

↓

– – –

Ч

2

↓

– – –

●

2

↓

– – –

Ч

2

↓

– – –

●

2

↓

– – –

Ч

2

↓

– – –

●

2

↓

– – –

Ч

A

←

A

A

←

B

A

←

F

A

←

imm4

A

←

[X]

A

←

[X], X

←

X+1

A

←

[Y]

A

←

[Y], Y

←

Y+1

B

←

A

B

←

B

B

←

imm4

B

←

[X]

B

←

[X], X

←

X+1

B

←

[Y]

B

←

[Y], Y

←

Y+1

F

←

A

F

←

imm4

[X]

←

A

[X]

←

B

[X]

←

imm4

[X]

←

[Y]

[X]

←

[Y], Y

←

Y+1

[X]

←

A, X

←

X+1

[X]

←

B, X

←

X+1

[X]

←

imm4, X

←

X+1

[X]

←

[Y], X

←

X+1

[X]

←

[Y], X

←

X+1, Y

←

Y+1

[Y]

←

A

[Y]

←

B

[Y]

←

imm4

[Y]

←

[X]

[Y]

←

[X], X

←

X+1

[Y]

←

A, Y

←

Y+1

[Y]

←

B, Y

←

Y+1

[Y]

←

imm4, Y

←

Y+1

[Y]

←

[X], Y

←

Y+1

[Y]

←

[X], Y

←

Y+1, X

←

X+1

A

↔

B

A

↔

[X]

A

↔

[X], X

←

X+1

A

↔

[Y]

A

↔

[Y], Y

←

Y+1

B

↔

[X]

B

↔

[X], X

←

X+1

B

↔

[Y]

B

↔

[Y], Y

←

Y+1

99

99

99

100

100

101

100

101

99

99

100

100

101

100

101

99

100

101

101

102

103

104

102

102

103

104

105

101

101

102

103

104

102

102

103

104

105

90

91

91

91

91

91

91

91

91

Mnemonic

Machine code

Operation

Cycle

Page

Flag

EXT.

mode

12

E I C Z

11 10 9 8 7 6 5 4 3 2 1 0

↔ ↔ ↔ ↔

↔ ↔ ↔ ↔

4-bit data transfer