Epson S1C63000 User Manual

Page 38

32

EPSON

S1C63000 CORE CPU MANUAL

CHAPTER 3: CPU OPERATION

During SLEEP status, as in the HALT status, the contents of the registers in the CPU that have been set

before shifting are maintained if rated voltage is supplied.

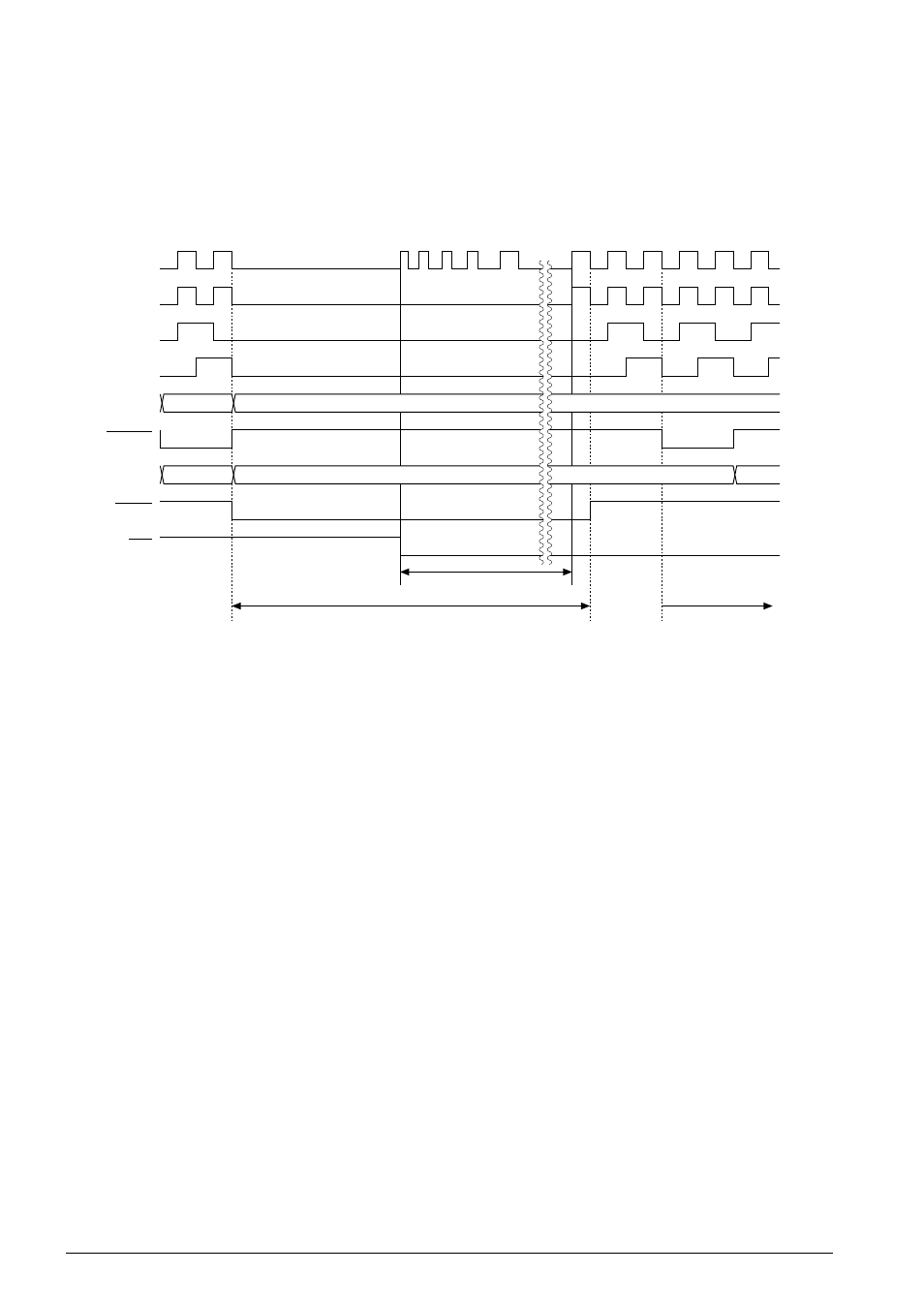

Figure 3.6.2.1 shows the sequence of shifting to the SLEEP status and restarting.

When an interrupt that releases the SLEEP status is generated, the oscillation circuit begins to oscillate.

When the oscillation starts, the CLK input to the CPU is masked by the peripheral circuit and the input to

the CPU begins after stabilization waiting time (several 10 msec–several msec) has elapsed. The CPU

samples the interrupt at the falling edge of the initially input CLK and starts the interrupt processing.

OSC

CLK

PK

PL

PC

FETCH

DBS1/0

STOP

IRQ

T1

SLP

pc

0

2

pc+1

Interrupt processing

T2 T3 T4

DUMMY

ANY

T1T2 T3 T4

SLEEP status

Oscillation stable

waiting time

Fig. 3.6.2.1 Sequence of the shift to SLEEP status and restarting