4 detailed explanation of instructions – Epson S1C63000 User Manual

Page 66

60

EPSON

S1C63000 CORE CPU MANUAL

CHAPTER 4: INSTRUCTION SET

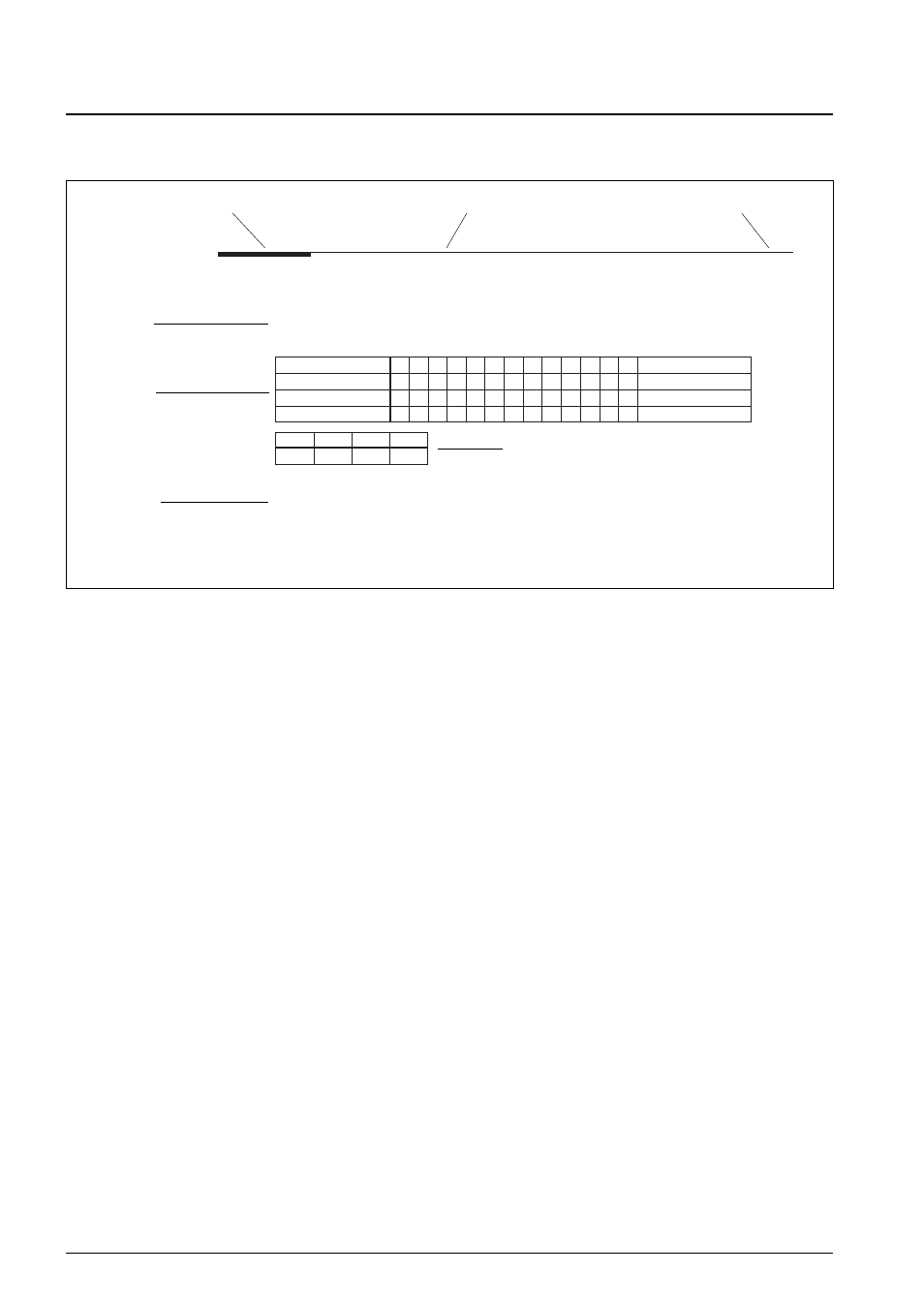

Add with carry r' reg. to r reg.

1 cycle

Function:

r

←

r + r' + C

Adds the content of the r' register (A or B) and carry (C) to the r register (A or B).

Code:

Mnemonic

MSB

LSB

ADC %A,%A

1

1

0

0

1

1

1

1

1

0

0

0

X

19F0H, (19F1H)

ADC %A,%B

1

1

0

0

1

1

1

1

1

0

0

1

X

19F2H, (19F3H)

ADC %B,%A

1

1

0

0

1

1

1

1

1

0

1

0

X

19F4H, (19F5H)

ADC %B,%B

1

1

0

0

1

1

1

1

1

0

1

1

X

19F6H, (19F7H)

Flags:

E

I

C

Z

↓

–

↕

↕

Mode:

Src: Register direct

Dst: Register direct

Extended addressing: Invalid

ADC %r,%r'

4.4 Detailed Explanation of Instructions

This section explains the individual instructions in alphabetic order according to the following format.

View of the explanation

Number of bus cycles

Mnemonic meaning

Mnemonic

Function

explanation

Mnemonic

and

object codes

Addressing

mode

Src indicates the source

and Dst indicates the

destination

The meaning of the symbols are the same as for the instruction list.

The following symbols are used to explain two or more registers as aggregations.

r .........

Data registers A, B, or flag register F

ir ........

Index registers X or Y

rr ........

Index registers XL, XH, YL or YH

sp .......

Stack pointers SP1 or SP2

Status of the flag

–

Does not change

↓

Reset

↑

Set

↕

Set/reset