Stack operation, Branch control, System control – Epson S1C63000 User Manual

Page 53

S1C63000 CORE CPU MANUAL

EPSON

47

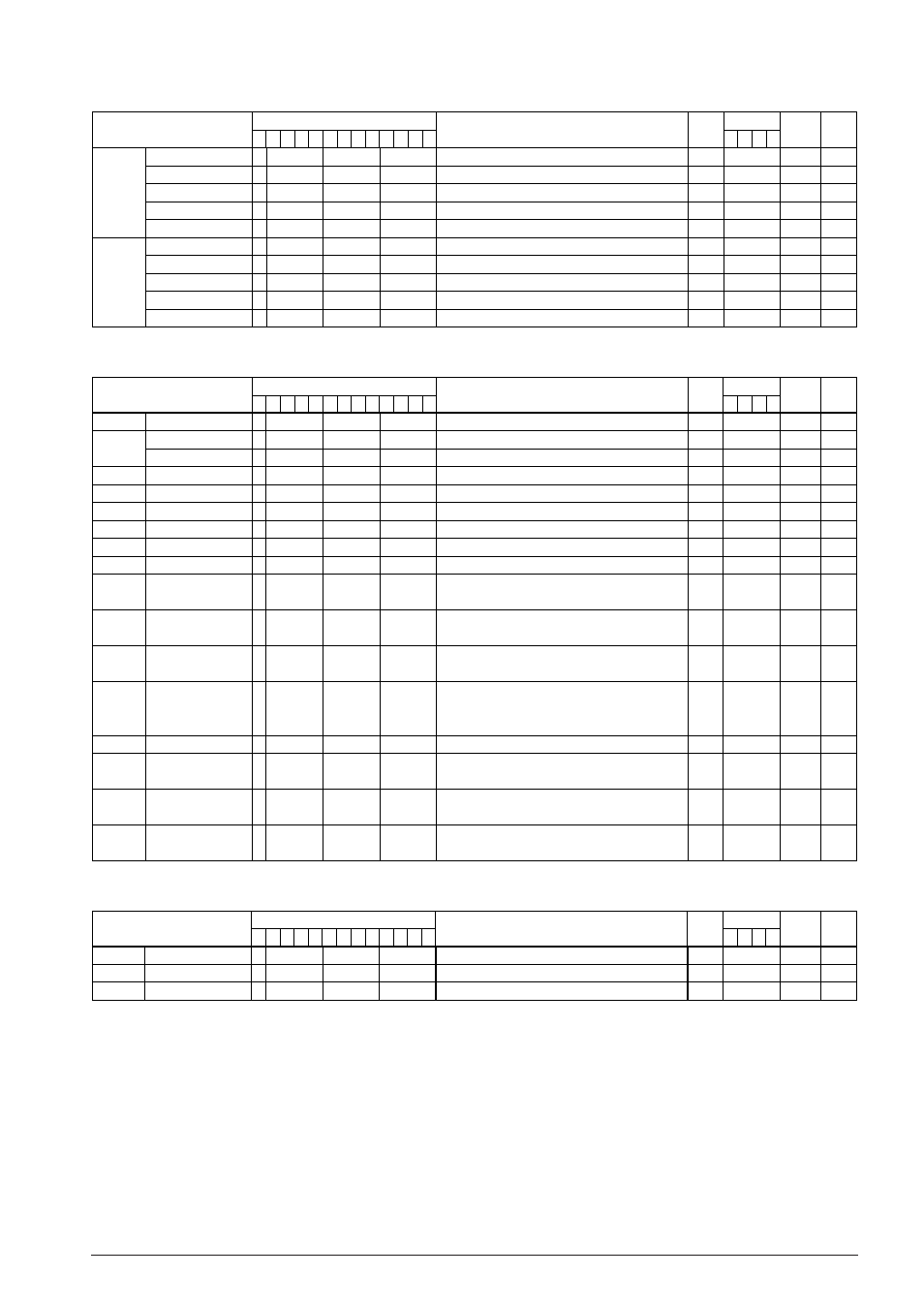

CHAPTER 4: INSTRUCTION SET

Note: • The extended addressing (combined with the E flag) is available only for the instructions indi-

cated with

●

●

in the EXT. mode row. Operation of other instructions (indicated with

×

) cannot be

guaranteed, therefore do not write data to the EXT register or do not set the E flag immediately

before those instructions.

• X in the machine code row indicates that the bit is valid even though it is "0" or "1", but the

assembler generates it as "0". When entering the code directly, such as for debugging, "0"

should be entered.

PUSH

%A

%B

%F

%X

%Y

POP

%A

%B

%F

%X

%Y

1 1 1 1 1 1 1 1 0 0 1 1 1

1 1 1 1 1 1 1 1 0 0 1 1 0

1 1 1 1 1 1 1 1 0 0 1 0 1

1 1 1 1 1 1 1 1 0 0 0 0 1

1 1 1 1 1 1 1 1 0 0 0 1 X

1 1 1 1 1 1 1 1 0 1 1 1 1

1 1 1 1 1 1 1 1 0 1 1 1 0

1 1 1 1 1 1 1 1 0 1 1 0 1

1 1 1 1 1 1 1 1 0 1 0 0 1

1 1 1 1 1 1 1 1 0 1 0 1 X

1

↓

– – –

Ч

1

↓

– – –

Ч

1

↓

– – –

Ч

1

↓

– – –

Ч

1

↓

– – –

Ч

1

↓

– – –

Ч

1

↓

– – –

Ч

1

Ч

1

↓

– – –

Ч

1

↓

– – –

Ч

[SP2-1]

←

A, SP2

←

SP2-1

[SP2-1]

←

B, SP2

←

SP2-1

[SP2-1]

←

F, SP2

←

SP2-1

([(SP1-1)

∗

4+3]~[(SP1-1)

∗

4])

←

X, SP1

←

SP1-1

([(SP1-1)

∗

4+3]~[(SP1-1)

∗

4])

←

Y, SP1

←

SP1-1

A

←

[SP2], SP2

←

SP2+1

B

←

[SP2], SP2

←

SP2+1

F

←

[SP2], SP2

←

SP2+1

X

←

([SP1

∗

4+3]~[SP1

∗

4]), SP1

←

SP1+1

Y

←

([SP1

∗

4+3]~[SP1

∗

4]), SP1

←

SP1+1

Mnemonic

Machine code

Operation

Cycle

Page

Flag

EXT.

mode

12

E I C Z

11 10 9 8 7 6 5 4 3 2 1 0

Stack operation

↔ ↔ ↔ ↔

117

117

117

118

118

116

116

116

117

117

JR

sign8

JR

%A

%BA

JR

[00addr6]

JRC

sign8

JRNC

sign8

JRZ

sign8

JRNZ

sign8

JP

%Y

CALZ

imm8

CALR

sign8

CALR

[00addr6]

INT

imm6

RET

RETS

RETD

imm8

RETI

0 0 0 0 0 s7 s6 s5 s4 s3 s2 s1 s0

1 1 1 1 1 1 1 1 1 0 0 0 1

1 1 1 1 1 1 1 1 1 0 0 0 0

1 1 1 1 1 0 1 a5 a4 a3 a2 a1 a0

0 0 1 0 0 s7 s6 s5 s4 s3 s2 s1 s0

0 0 1 0 1 s7 s6 s5 s4 s3 s2 s1 s0

0 0 1 1 0 s7 s6 s5 s4 s3 s2 s1 s0

0 0 1 1 1 s7 s6 s5 s4 s3 s2 s1 s0

1 1 1 1 1 1 1 1 1 0 0 1 X

0 0 0 1 1 i7 i6 i5 i4 i3 i2 i1 i0

0 0 0 1 0 s7 s6 s5 s4 s3 s2 s1 s0

1 1 1 1 1 0 0 a5 a4 a3 a2 a1 a0

1 1 1 1 1 1 0 i5 i4 i3 i2 i1 i0

1 1 1 1 1 1 1 1 1 1 0 X 0

1 1 1 1 1 1 1 1 1 1 0 1 1

1 0 0 0 1 i7 i6 i5 i4 i3 i2 i1 i0

1 1 1 1 1 1 1 1 1 1 0 0 1

1

↓

– – –

●

1

↓

– – –

Ч

1

↓

– – –

Ч

2

↓

– – –

Ч

1

↓

– – –

●

1

↓

– – –

●

1

↓

– – –

●

1

↓

– – –

●

1

↓

– – –

Ч

1

↓

– – –

Ч

1

↓

– – –

●

2

↓

– – –

Ч

3

↓

– – –

Ч

1

↓

– – –

Ч

2

↓

– – –

Ч

3

↓

– – –

Ч

2

Ч

PC

←

PC+sign8+1 (sign8=-128~127)

PC

←

PC+A+1

PC

←

PC+BA+1

PC

←

PC+[00addr6]+1

If C=1 then PC

←

PC+sign8+1 (sign8=-128~127)

If C=0 then PC

←

PC+sign8+1 (sign8=-128~127)

If Z=1 then PC

←

PC+sign8+1 (sign8=-128~127)

If Z=0 then PC

←

PC+sign8+1 (sign8=-128~127)

PC

←

Y

([(SP1-1)

∗

4+3]~[(SP1-1)

∗

4])

←

PC+1,

SP1

←

SP1-1, PC

←

imm8

([(SP1-1)

∗

4+3]~[(SP1-1)

∗

4])

←

PC+1,

SP1

←

SP1-1, PC

←

PC+sign8+1 (sign8=-128~127)

([(SP1-1)

∗

4+3]~[(SP1-1)

∗

4])

←

PC+1,

SP1

←

SP1-1, PC

←

PC+[00addr6]+1

[SP2-1]

←

F, SP2

←

SP2-1

([(SP1-1)

∗

4+3]~[(SP1-1)

∗

4])

←

PC+1,

SP1

←

SP1-1, PC

←

imm6 (imm6=0100H~013FH)

PC

←

([SP1

∗

4+3]~[SP1

∗

4]), SP1

←

SP1+1

PC

←

([SP1

∗

4+3]~[SP1

∗

4]), SP1

←

SP1+1

PC

←

PC+1

PC

←

([SP1

∗

4+3]~[SP1

∗

4]), SP1

←

SP1+1

[X]

←

i3~0, [X+1]

←

i7~4, X

←

X+2

PC

←

([SP1

∗

4+3]~[SP1

∗

4]), SP1

←

SP1+1

F

←

[SP2], SP2

←

SP2+1

Mnemonic

Machine code

Operation

Cycle

Page

Flag

EXT.

mode

12

E I C Z

11 10 9 8 7 6 5 4 3 2 1 0

Branch control

↔ ↔ ↔ ↔

97

95

96

96

97

98

99

98

95

83

82

82

94

118

120

119

119

HALT

SLP

NOP

1 1 1 1 1 1 1 1 1 1 1 0 0

1 1 1 1 1 1 1 1 1 1 1 0 1

1 1 1 1 1 1 1 1 1 1 1 1 X

2

↓

– – –

Ч

2

↓

– – –

Ч

1

↓

– – –

Ч

Halt

Sleep

No operation (PC

←

PC+1)

Mnemonic

Machine code

Operation

Cycle

Page

Flag

EXT.

mode

12

E I C Z

11 10 9 8 7 6 5 4 3 2 1 0

System control

92

133

111