Push %ir – Epson S1C63000 User Manual

Page 124

118

EPSON

S1C63000 CORE CPU MANUAL

CHAPTER 4: INSTRUCTION SET

PUSH %ir

Push ir reg. onto stack

1 cycle

Function:

([(SP1-1)*4+3]~[(SP1-1)*4])

←

ir, SP1

←

SP1 -1

Decrements the stack pointer SP1, then stores the content of the ir register (X or Y) into the

addresses (4 words) indicated by the SP1 (SP1 indicates the lowest address).

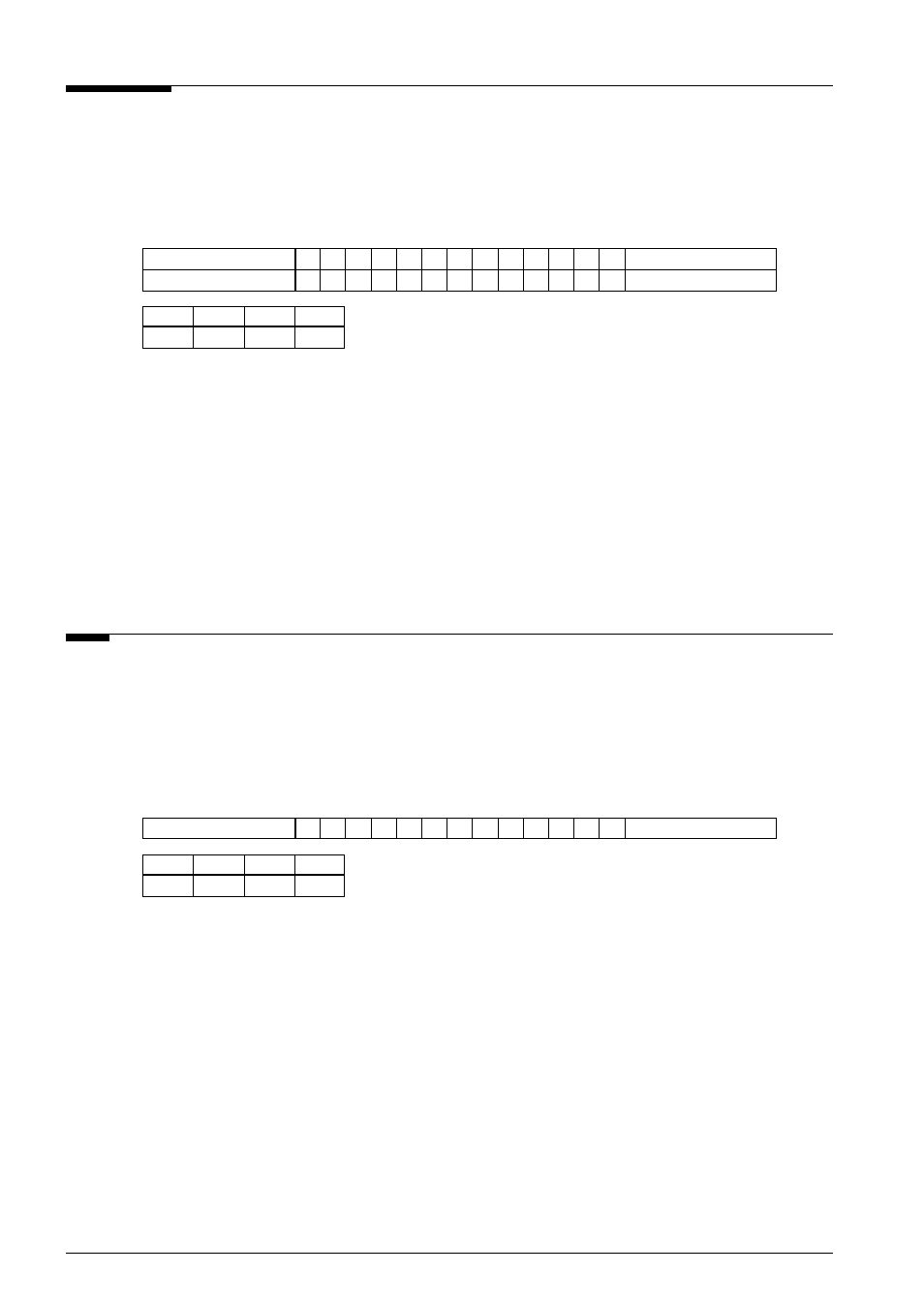

Code:

Mnemonic

MSB

LSB

PUSH %X

1

1

1

1

1

1

1

1

0

0

0

0

1

1FE1H

PUSH %Y

1

1

1

1

1

1

1

1

0

0

0

1

X

1FE2H, (1FE3H)

Flags:

E

I

C

Z

↓

–

–

–

Mode:

Register direct

Extended addressing: Invalid

RET

Return from subroutine

1 cycle

Function:

PC

←

([SP1*4+3]~[SP1*4]), SP1

←

SP1 +1

Loads the 16-bit data (return address) that has been stored in the addresses (4 words) indicated

by the stack pointer SP1 (SP1 indicates the lowest address) into the PC to return from the

subroutine. The SP1 is incremented.

Code:

Mnemonic

MSB

LSB

RET

1

1

1

1

1

1

1

1

1

1

0

X

0

1FF8H, (1FFAH)

Flags:

E

I

C

Z

↓

–

–

–