3 branch instructions – Epson S1C63000 User Manual

Page 18

12

EPSON

S1C63000 CORE CPU MANUAL

CHAPTER 2: ARCHITECTURE

2.2.3 Branch instructions

Various branch instructions are provided for program repeat and subroutine calls that change a sequen-

tial program flow controlled with the PC. The branch instruction modifies the PC to branch the program

to an optional address. The types of the branch instructions are classified as follows, according to their

operation differences.

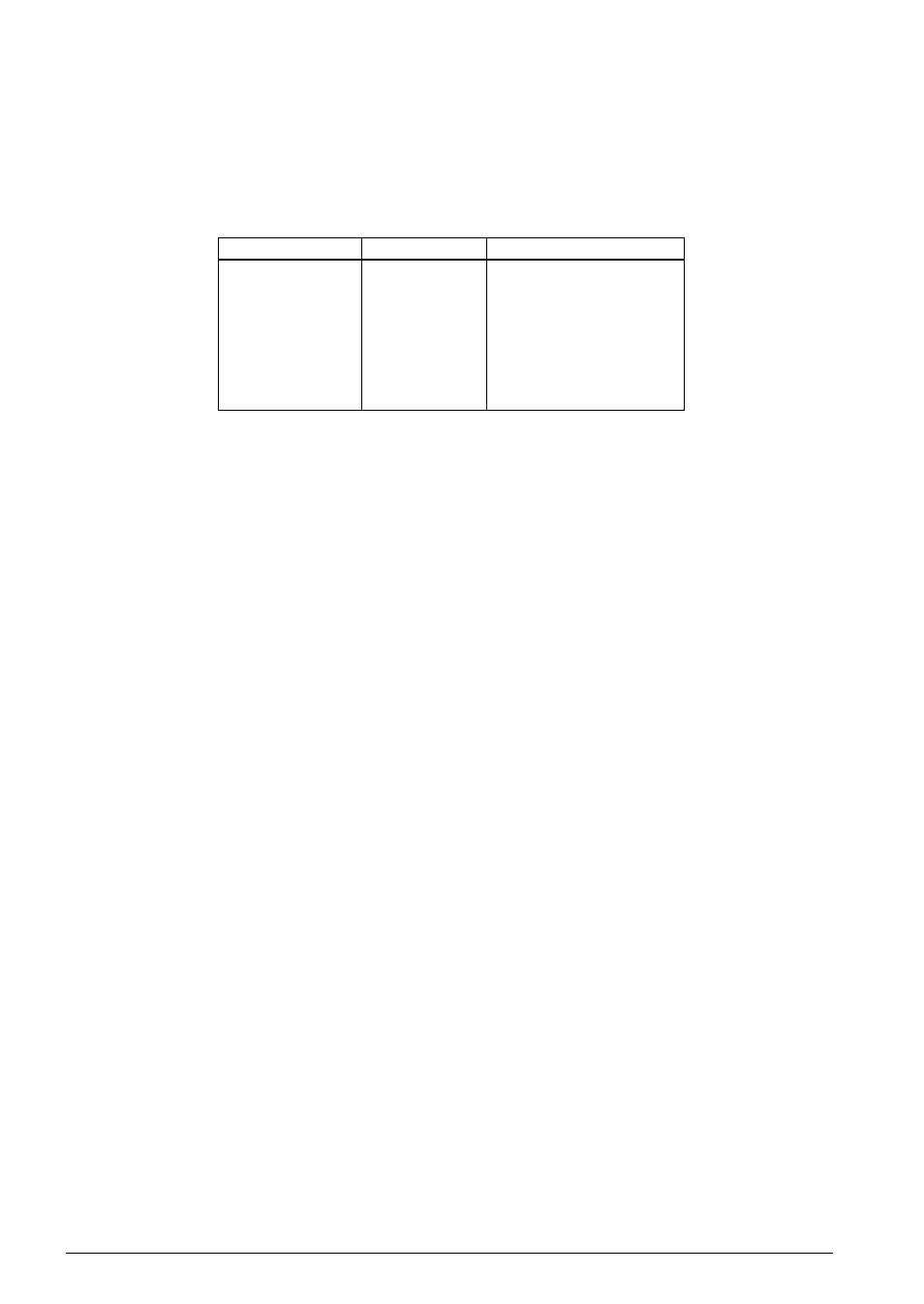

Table 2.2.3.1 Types of branch instructions

• PC relative jump instructions (JR)

The PC relative jump instruction adds the relative address specified in the operand to the PC that has

indicated the next address, and branches to that address. It permits relocatable programming.

The relative address to be specified in the operand is a displacement from the PC value (address of the

next instruction) when the branch instruction is executed to the branch destination address. When

programming using the S1C63 Family assembler, it is not necessary to calculate displacements

because a branch destination address can be defined as a label and it can be used as an operand.

However, the range of branch destination addresses is different depending on the number of data bits

that are handled as relative addresses.

The following explains the PC relative jump instructions and the relative addresses.

(1) Instructions with a signed 8-bit immediate data sign8 that specifies a relative address

Unconditional jump

JR sign8

Conditional jump

JRC sign8 JRNC sign8 JRZ sign8 JRNZ sign8

These instructions branch the program sequence with the sign8 specified in the operand as a

signed 8-bit relative address. The range that can be branched is from the next instruction address -

128 to +127. A value within the range from -128 to +127 should be used if specifying a value for

jumping in the assembler. Generally branch destination labels such as "JR LABEL" are used, and

they are expanded into the actual address by the assembler.

These instructions permit the extended addressing with the E flag, and the 8-bit relative address

can be extended into 16 bits (the contents of the EXT register become the high-order 8 bits). In this

case, the range that can be branched is from the next instruction address -32768 to +32767. Conse-

quently, in the extended addressing mode these instructions can branch the entire 64K program

memory.

Examples:

JR

-100

...Jumps to the instruction 99 steps before

LDB

%EXT,100

...(100

×

256) = 25600

JR

100

...Jumps to the instruction 25701 steps after

The unconditional jump instruction "JR sign8" jumps to the branch destination unconditionally

when it is executed.

The conditional jump instructions jump according to the status of C flag or the Z flag.

JRC

sign8

...Jumps if the C flag is "1", or executes the next instruction if the C flag is "0"

JRNC sign8

...Jumps if the C flag is "0", or executes the next instruction if the C flag is "1"

JRZ

sign8

...Jumps if the Z flag is "1", or executes the next instruction if the Z flag is "0"

JRNZ sign8

...Jumps if the Z flag is "0", or executes the next instruction if the Z flag is "1"

Type

PC relative jump

PC relative jump

Indirect jump

Absolute call

PC relative call

Return

Software interrupt

Condition

Instruction

JR

JRC, JRNC, JRZ, JRNZ

JP

CALZ

CALR

RET, RETS, RETD, RETI

INT

Unconditional

Conditional

Unconditional

Unconditional

Unconditional

Unconditional

Unconditional