Epson S1C63000 User Manual

Page 56

50

EPSON

S1C63000 CORE CPU MANUAL

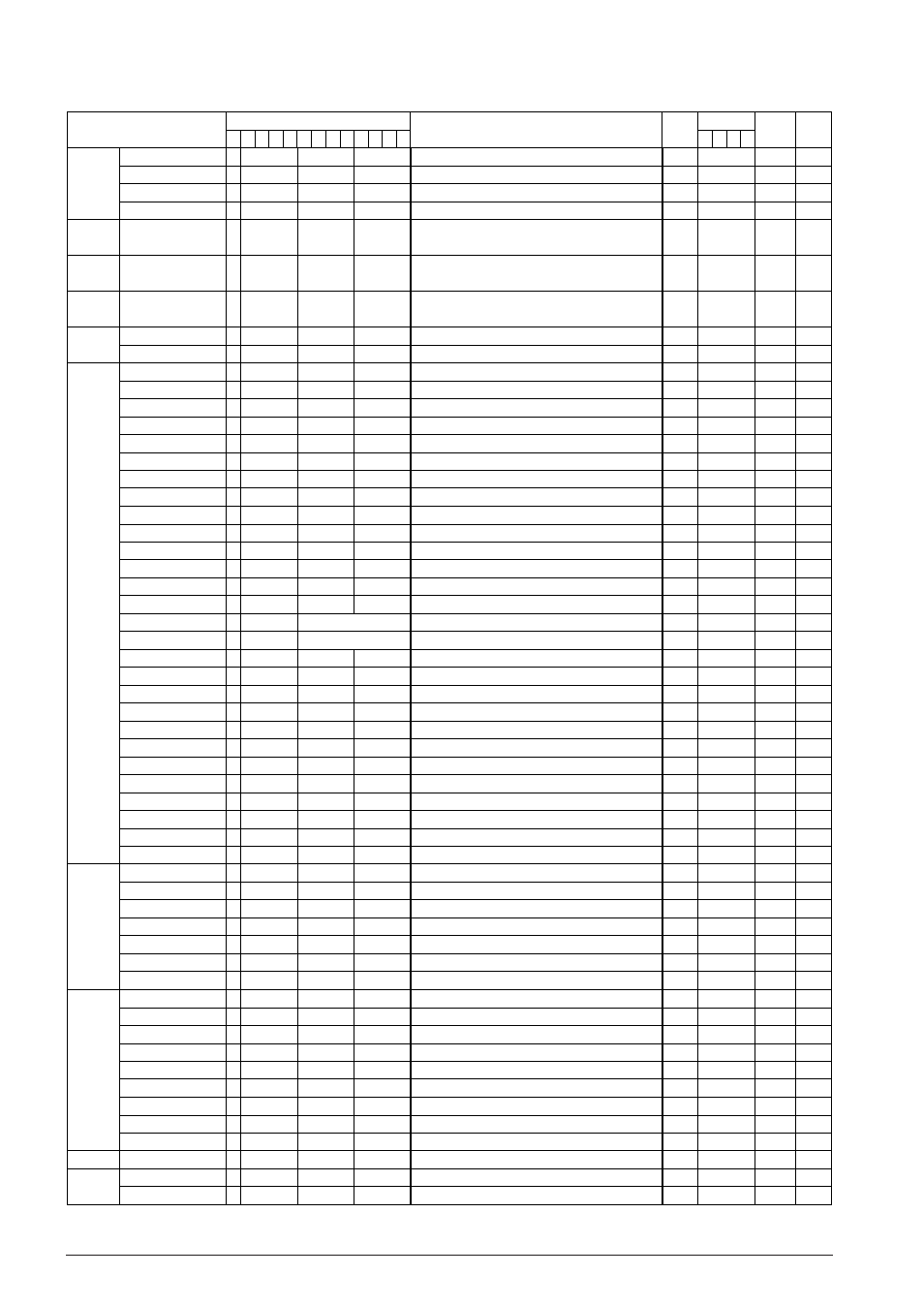

CHAPTER 4: INSTRUCTION SET

BIT

[%Y],imm4

[%Y]+,%A

[%Y]+,%B

[%Y]+,imm4

CALR

[00addr6]

CALR

sign8

CALZ

imm8

CLR

[00addr6],imm2

[FFaddr6],imm2

CMP

%A,%A

%A,%B

%A,imm4

%A,[%X]

%A,[%X]+

%A,[%Y]

%A,[%Y]+

%B,%A

%B,%B

%B,imm4

%B,[%X]

%B,[%X]+

%B,[%Y]

%B,[%Y]+

%X,imm8

%Y,imm8

[%X],%A

[%X],%B

[%X],imm4

[%X]+,%A

[%X]+,%B

[%X]+,imm4

[%Y],%A

[%Y],%B

[%Y],imm4

[%Y]+,%A

[%Y]+,%B

[%Y]+,imm4

DEC

%SP1

%SP2

[%X],n4

[%X]+,n4

[%Y],n4

[%Y]+,n4

[00addr6]

EX

%A,%B

%A,[%X]

%A,[%X]+

%A,[%Y]

%A,[%Y]+

%B,[%X]

%B,[%X]+

%B,[%Y]

%B,[%Y]+

HALT

INC

%SP1

%SP2

1 1 0 1 0 1 0 1 0 i3 i2 i1 i0

1 1 0 1 0 1 1 1 0 1 0 1 1

1 1 0 1 0 1 1 1 0 1 1 1 1

1 1 0 1 0 1 0 1 1 i3 i2 i1 i0

1 1 1 1 1 0 0 a5 a4 a3 a2 a1 a0

0 0 0 1 0 s7 s6 s5 s4 s3 s2 s1 s0

0 0 0 1 1 i7 i6 i5 i4 i3 i2 i1 i0

1 0 1 0 0 i1 i0 a5 a4 a3 a2 a1 a0

1 0 1 0 1 i1 i0 a5 a4 a3 a2 a1 a0

1 1 1 1 0 0 1 1 1 X 0 0 0

1 1 1 1 0 0 1 1 1 X 0 1 0

1 1 1 1 0 0 1 0 0 i3 i2 i1 i0

1 1 1 1 0 0 1 1 0 0 0 0 0

1 1 1 1 0 0 1 1 0 0 0 0 1

1 1 1 1 0 0 1 1 0 0 0 1 0

1 1 1 1 0 0 1 1 0 0 0 1 1

1 1 1 1 0 0 1 1 1 X 1 0 0

1 1 1 1 0 0 1 1 1 X 1 1 0

1 1 1 1 0 0 1 0 1 i3 i2 i1 i0

1 1 1 1 0 0 1 1 0 0 1 0 0

1 1 1 1 0 0 1 1 0 0 1 0 1

1 1 1 1 0 0 1 1 0 0 1 1 0

1 1 1 1 0 0 1 1 0 0 1 1 1

0 1 1 1 0 [

FFH - imm8

]

0 1 1 1 1 [

FFH - imm8

]

1 1 1 1 0 0 1 1 0 1 0 0 0

1 1 1 1 0 0 1 1 0 1 1 0 0

1 1 1 1 0 0 0 0 0 i3 i2 i1 i0

1 1 1 1 0 0 1 1 0 1 0 0 1

1 1 1 1 0 0 1 1 0 1 1 0 1

1 1 1 1 0 0 0 0 1 i3 i2 i1 i0

1 1 1 1 0 0 1 1 0 1 0 1 0

1 1 1 1 0 0 1 1 0 1 1 1 0

1 1 1 1 0 0 0 1 0 i3 i2 i1 i0

1 1 1 1 0 0 1 1 0 1 0 1 1

1 1 1 1 0 0 1 1 0 1 1 1 1

1 1 1 1 0 0 0 1 1 i3 i2 i1 i0

1 1 1 1 1 1 1 1 0 0 0 0 0

1 1 1 1 1 1 1 1 0 0 1 0 0

1 1 1 0 0 1 0 0 0 n3 n2 n1 n0

1 1 1 0 0 1 0 0 1 n3 n2 n1 n0

1 1 1 0 0 1 0 1 0 n3 n2 n1 n0

1 1 1 0 0 1 0 1 1 n3 n2 n1 n0

1 0 0 0 0 0 0 a5 a4 a3 a2 a1 a0

1 1 1 1 1 1 1 1 1 0 1 1 1

1 0 0 0 0 1 1 1 1 1 0 0 0

1 0 0 0 0 1 1 1 1 1 0 0 1

1 0 0 0 0 1 1 1 1 1 0 1 0

1 0 0 0 0 1 1 1 1 1 0 1 1

1 0 0 0 0 1 1 1 1 1 1 0 0

1 0 0 0 0 1 1 1 1 1 1 0 1

1 0 0 0 0 1 1 1 1 1 1 1 0

1 0 0 0 0 1 1 1 1 1 1 1 1

1 1 1 1 1 1 1 1 1 1 1 0 0

1 1 1 1 1 1 1 1 0 1 0 0 0

1 1 1 1 1 1 1 1 0 1 1 0 0

1

↓

– –

●

1

↓

– –

Ч

1

↓

– –

Ч

1

↓

– –

Ч

2

↓

– – –

Ч

1

↓

– – –

●

1

↓

– – –

Ч

2

↓

– –

Ч

2

↓

– –

Ч

1

↓

–

↓ ↑

Ч

1

↓

–

Ч

1

↓

–

Ч

1

↓

–

●

1

↓

–

Ч

1

↓

–

●

1

↓

–

Ч

1

↓

–

Ч

1

↓

–

↓ ↑

Ч

1

↓

–

Ч

1

↓

–

●

1

↓

–

Ч

1

↓

–

●

1

↓

–

Ч

1

↓

–

●

1

↓

–

●

1

↓

–

●

1

↓

–

●

1

↓

–

●

1

↓

–

Ч

1

↓

–

Ч

1

↓

–

Ч

1

↓

–

●

1

↓

–

●

1

↓

–

●

1

↓

–

Ч

1

↓

–

Ч

1

↓

–

Ч

1

↓

– –

Ч

1

↓

– –

Ч

2

↓

–

●

2

↓

–

Ч

2

↓

–

●

2

↓

–

Ч

2

↓

–

Ч

1

↓

– – –

Ч

2

↓

– – –

●

2

↓

– – –

Ч

2

↓

– – –

●

2

↓

– – –

Ч

2

↓

– – –

●

2

↓

– – –

Ч

2

↓

– – –

●

2

↓

– – –

Ч

2

↓

– – –

Ч

1

↓

– –

Ч

1

↓

– –

Ч

↔

↔

[Y]

∧

imm4

[Y]

∧

A, Y

←

Y+1

[Y]

∧

B, Y

←

Y+1

[Y]

∧

imm4, Y

←

Y+1

([(SP1-1)

∗

4+3]~[(SP1-1)

∗

4])

←

PC+1,

SP1

←

SP1-1, PC

←

PC+[00addr6]+1

([(SP1-1)

∗

4+3]~[(SP1-1)

∗

4])

←

PC+1,

SP1

←

SP1-1, PC

←

PC+sign8+1 (sign8=-128~127)

([(SP1-1)

∗

4+3]~[(SP1-1)

∗

4])

←

PC+1,

SP1

←

SP1-1, PC

←

imm8

[00addr6]

←

[00addr6]

∧

not (2

imm2

)

[FFaddr6]

←

[FFaddr6]

∧

not (2

imm2

)

A-A

A-B

A-imm4

A-[X]

A-[X], X

←

X+1

A-[Y]

A-[Y], Y

←

Y+1

B-A

B-B

B-imm4

B-[X]

B-[X], X

←

X+1

B-[Y]

B-[Y], Y

←

Y+1

X-imm8 (imm8=0~255)

Y-imm8 (imm8=0~255)

[X]-A

[X]-B

[X]-imm4

[X]-A, X

←

X+1

[X]-B, X

←

X+1

[X]-imm4, X

←

X+1

[Y]-A

[Y]-B

[Y]-imm4

[Y]-A, Y

←

Y+1

[Y]-B, Y

←

Y+1

[Y]-imm4, Y

←

Y+1

SP1

←

SP1-1

SP2

←

SP2-1

[X]

←

N's adjust ([X]-1)

[X]

←

N's adjust ([X]-1), X

←

X+1

[Y]

←

N's adjust ([Y]-1)

[Y]

←

N's adjust ([Y]-1), Y

←

Y+1

[00addr6]

←

[00addr6]-1

A

↔

B

A

↔

[X]

A

↔

[X], X

←

X+1

A

↔

[Y]

A

↔

[Y], Y

←

Y+1

B

↔

[X]

B

↔

[X], X

←

X+1

B

↔

[Y]

B

↔

[Y], Y

←

Y+1

Halt

SP1

←

SP1+1

SP2

←

SP2+1

Mnemonic

Machine code

Operation

Cycle

Page

Flag

EXT.

mode

12

E I C Z

11 10 9 8 7 6 5 4 3 2 1 0

↔

↔

↔

↔

↔

↔

↔ ↔

↔

↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

81

80

80

81

82

82

83

83

83

84

84

84

85

85

85

85

84

84

84

85

85

85

85

88

88

86

86

87

86

86

87

86

86

87

86

86

87

90

90

89

89

89

89

88

90

91

91

91

91

91

91

91

91

92

94

94