And [%ir],imm4, And [%ir]+,imm4 – Epson S1C63000 User Manual

Page 83

S1C63000 CORE CPU MANUAL

EPSON

77

CHAPTER 4: INSTRUCTION SET

AND [%ir],imm4

Logical AND of immediate data imm4 and location [ir reg.]

2 cycles

Function:

[ir]

←

[ir]

∧

imm4

Performs a logical AND operation of the 4-bit immediate data imm4 and the content of the

data memory addressed by the ir register (X or Y), and stores the result in that address.

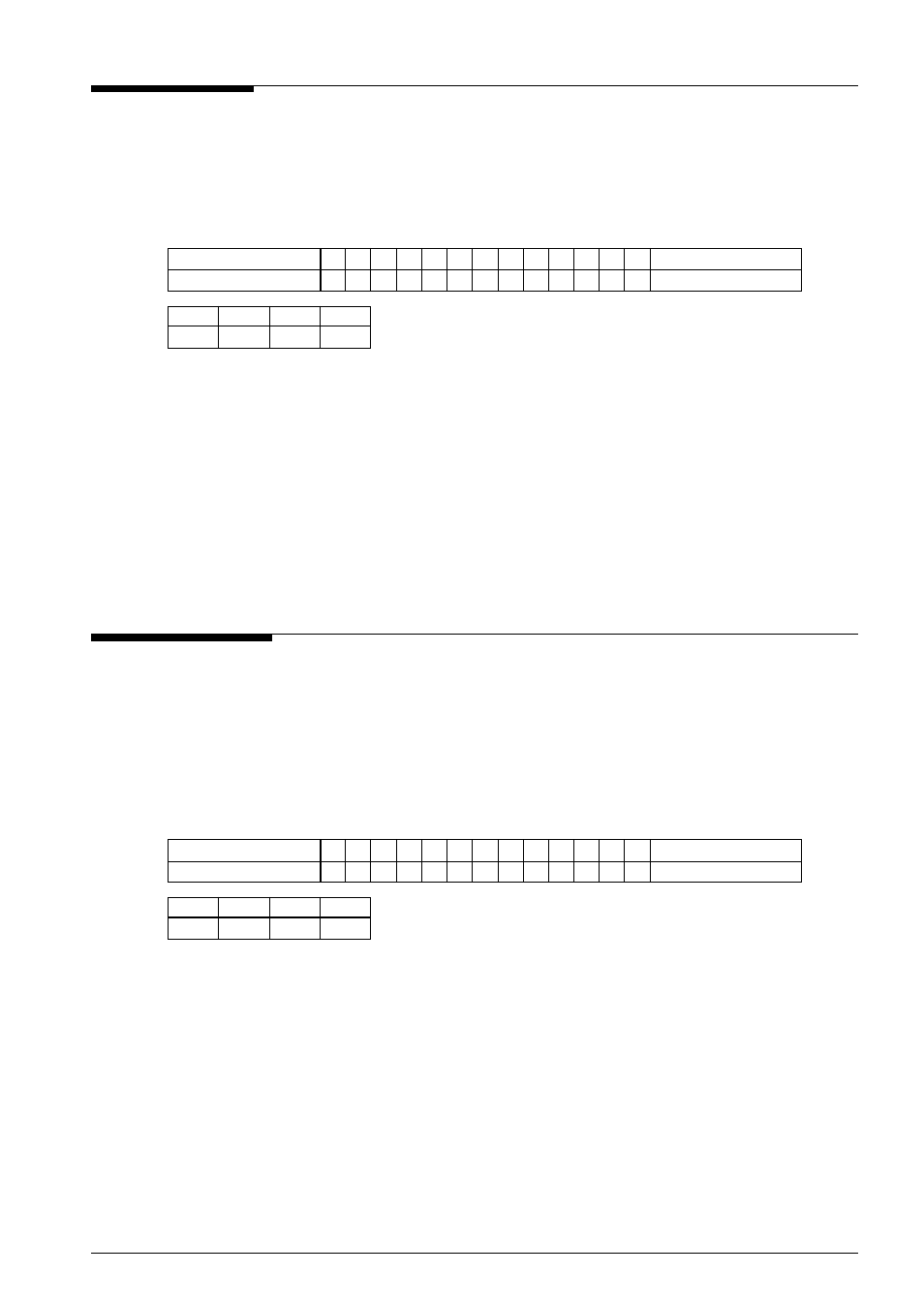

Code:

Mnemonic

MSB

LSB

AND [%X],imm4

1

1

0

1

0

0

0

0

0 i3 i2 i1 i0

1A00H–1A0FH

AND [%Y],imm4

1

1

0

1

0

0

0

1

0 i3 i2 i1 i0

1A20H–1A2FH

Flags:

E

I

C

Z

↓

–

–

↕

Mode:

Src: Immediate data

Dst: Register indirect

Extended addressing: Valid

Extended

LDB

%EXT,imm8

operation:

AND

[%X],imm4

[00imm8]

←

[00imm8]

∧

imm4 (00imm8 = 0000H + 00H to FFH)

LDB

%EXT,imm8

AND

[%Y],imm4

[FFimm8]

←

[FFimm8]

∧

imm4 (FFimm8 = FF00H + 00H to FFH)

AND [%ir]+,imm4

Logical AND of immediate data imm4 and location [ir reg.] and increment ir reg. 2 cycles

Function:

[ir]

←

[ir]

∧

imm4, ir

←

ir + 1

Performs a logical AND operation of the 4-bit immediate data imm4 and the content of the

data memory addressed by the ir register (X or Y), and stores the result in that address. Then

increments the ir register (X or Y). The flags change due to the operation result of the data

memory and the increment result of the ir register does not affect the flags.

Code:

Mnemonic

MSB

LSB

AND [%X]+,imm4

1

1

0

1

0

0

0

0

1 i3 i2 i1 i0

1A10H–1A1FH

AND [%Y]+,imm4

1

1

0

1

0

0

0

1

1 i3 i2 i1 i0

1A30H–1A3FH

Flags:

E

I

C

Z

↓

–

–

↕

Mode:

Src: Immediate data

Dst: Register indirect

Extended addressing: Invalid