And %r,[%ir] and %r,[%ir – Epson S1C63000 User Manual

Page 81

S1C63000 CORE CPU MANUAL

EPSON

75

CHAPTER 4: INSTRUCTION SET

AND %r,[%ir]

AND %r,[%ir]+

Logical AND of location [ir reg.] and r reg. and increment ir reg.

1 cycle

Function:

r

←

r

∧

[ir], ir

←

ir + 1

Performs a logical AND operation of the content of the data memory addressed by the ir

register (X or Y) and the content of the r register (A or B), and stores the result in the r register.

Then increments the ir register (X or Y). The flags change due to the operation result of the r

register and the increment result of the ir register does not affect the flags.

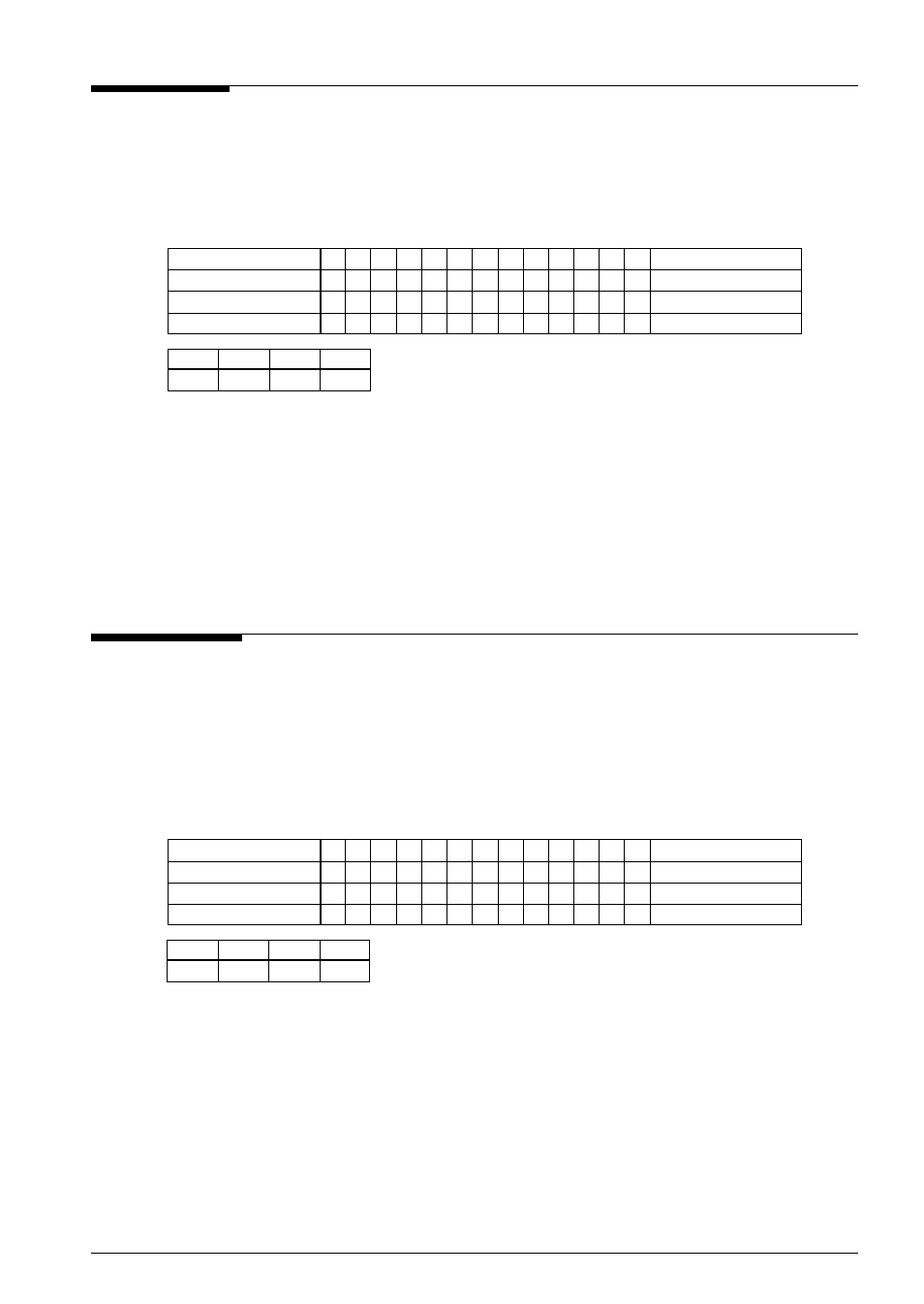

Code:

Mnemonic

MSB

LSB

AND %A,[%X]+

1

1

0

1

0

0

1

1

0

0

0

0

1

1A61H

AND %A,[%Y]+

1

1

0

1

0

0

1

1

0

0

0

1

1

1A63H

AND %B,[%X]+

1

1

0

1

0

0

1

1

0

0

1

0

1

1A65H

AND %B,[%Y]+

1

1

0

1

0

0

1

1

0

0

1

1

1

1A67H

Flags:

E

I

C

Z

↓

–

–

↕

Mode:

Src: Register indirect

Dst: Register direct

Extended addressing: Invalid

Logical AND of location [ir reg.] and r reg.

1 cycle

Function:

r

←

r

∧

[ir]

Performs a logical AND operation of the content of the data memory addressed by the ir

register (X or Y) and the content of the r register (A or B), and stores the result in the r register.

Code:

Mnemonic

MSB

LSB

AND %A,[%X]

1

1

0

1

0

0

1

1

0

0

0

0

0

1A60H

AND %A,[%Y]

1

1

0

1

0

0

1

1

0

0

0

1

0

1A62H

AND %B,[%X]

1

1

0

1

0

0

1

1

0

0

1

0

0

1A64H

AND %B,[%Y]

1

1

0

1

0

0

1

1

0

0

1

1

0

1A66H

Flags:

E

I

C

Z

↓

–

–

↕

Mode:

Src: Register indirect

Dst: Register direct

Extended addressing: Valid

Extended

LDB

%EXT,imm8

operation:

AND

%r,[%X]

r

←

r

∧

[00imm8] (00imm8 = 0000H + 00H to FFH)

LDB

%EXT,imm8

AND

%r,[%Y]

r

←

r

∧

[FFimm8] (FFimm8 = FF00H + 00H to FFH)