Epson S1C63000 User Manual

Page 60

54

EPSON

S1C63000 CORE CPU MANUAL

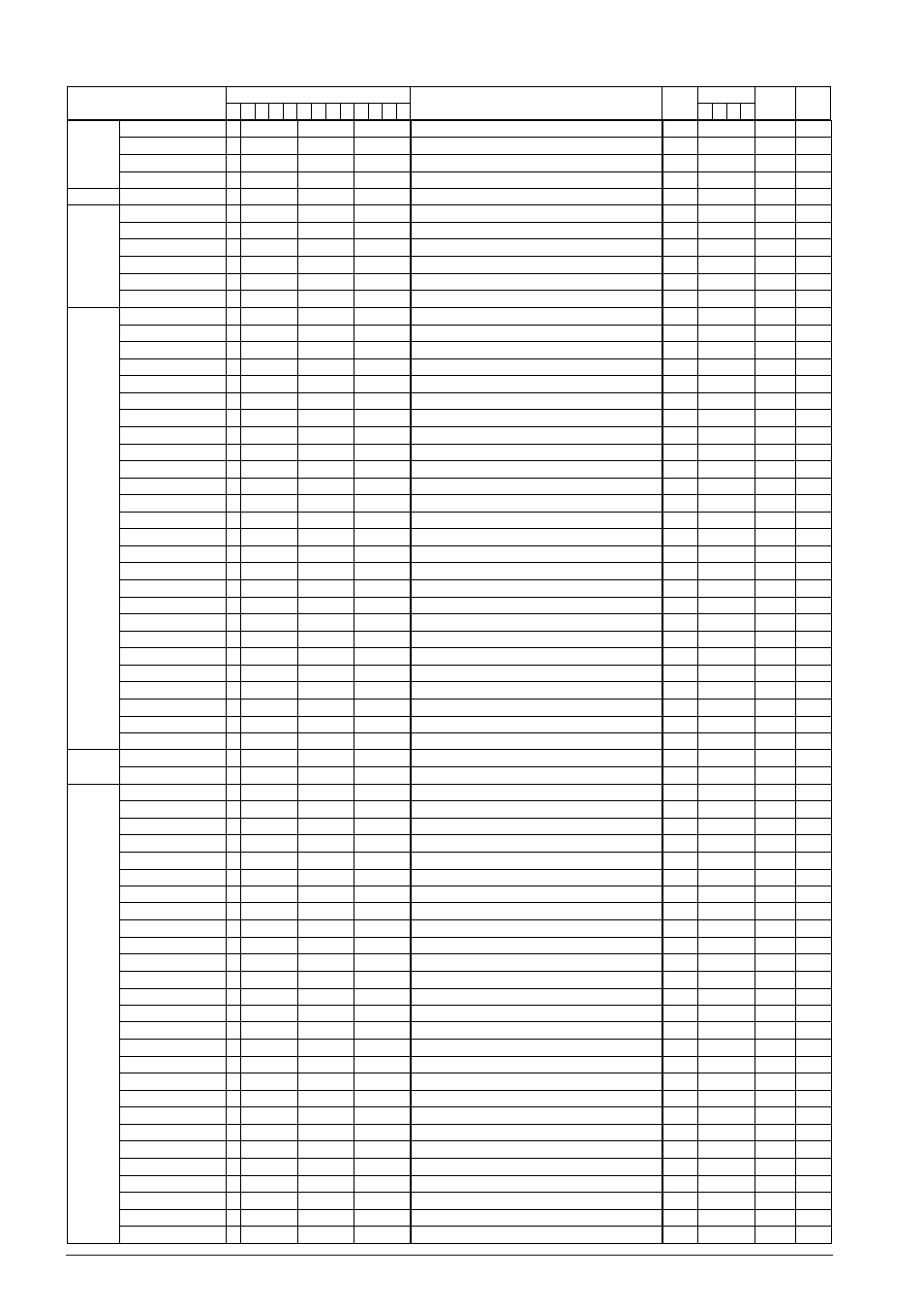

CHAPTER 4: INSTRUCTION SET

SLL

[%X]

[%X]+

[%Y]

[%Y]+

SLP

SRL

%A

%B

[%X]

[%X]+

[%Y]

[%Y]+

SUB

%A,%A

%A,%B

%A,imm4

%A,[%X]

%A,[%X]+

%A,[%Y]

%A,[%Y]+

%B,%A

%B,%B

%B,imm4

%B,[%X]

%B,[%X]+

%B,[%Y]

%B,[%Y]+

[%X],%A

[%X],%B

[%X],imm4

[%X]+,%A

[%X]+,%B

[%X]+,imm4

[%Y],%A

[%Y],%B

[%Y],imm4

[%Y]+,%A

[%Y]+,%B

[%Y]+,imm4

TST

[00addr6],imm2

[FFaddr6],imm2

XOR

%A,%A

%A,%B

%A,imm4

%A,[%X]

%A,[%X]+

%A,[%Y]

%A,[%Y]+

%B,%A

%B,%B

%B,imm4

%B,[%X]

%B,[%X]+

%B,[%Y]

%B,[%Y]+

%F,imm4

[%X],%A

[%X],%B

[%X],imm4

[%X]+,%A

[%X]+,%B

[%X]+,imm4

[%Y],%A

[%Y],%B

[%Y],imm4

[%Y]+,%A

[%Y]+,%B

[%Y]+,imm4

1 0 0 0 0 1 1 1 0 0 0 0 0

1 0 0 0 0 1 1 1 0 0 0 0 1

1 0 0 0 0 1 1 1 0 0 0 1 0

1 0 0 0 0 1 1 1 0 0 0 1 1

1 1 1 1 1 1 1 1 1 1 1 0 1

1 0 0 0 0 1 1 1 1 0 0 0 1

1 0 0 0 0 1 1 1 1 0 1 0 1

1 0 0 0 0 1 1 1 0 0 1 0 0

1 0 0 0 0 1 1 1 0 0 1 0 1

1 0 0 0 0 1 1 1 0 0 1 1 0

1 0 0 0 0 1 1 1 0 0 1 1 1

1 1 0 0 0 0 1 1 1 0 0 0 X

1 1 0 0 0 0 1 1 1 0 0 1 X

1 1 0 0 0 0 1 0 0 i3 i2 i1 i0

1 1 0 0 0 0 1 1 0 0 0 0 0

1 1 0 0 0 0 1 1 0 0 0 0 1

1 1 0 0 0 0 1 1 0 0 0 1 0

1 1 0 0 0 0 1 1 0 0 0 1 1

1 1 0 0 0 0 1 1 1 0 1 0 X

1 1 0 0 0 0 1 1 1 0 1 1 X

1 1 0 0 0 0 1 0 1 i3 i2 i1 i0

1 1 0 0 0 0 1 1 0 0 1 0 0

1 1 0 0 0 0 1 1 0 0 1 0 1

1 1 0 0 0 0 1 1 0 0 1 1 0

1 1 0 0 0 0 1 1 0 0 1 1 1

1 1 0 0 0 0 1 1 0 1 0 0 0

1 1 0 0 0 0 1 1 0 1 1 0 0

1 1 0 0 0 0 0 0 0 i3 i2 i1 i0

1 1 0 0 0 0 1 1 0 1 0 0 1

1 1 0 0 0 0 1 1 0 1 1 0 1

1 1 0 0 0 0 0 0 1 i3 i2 i1 i0

1 1 0 0 0 0 1 1 0 1 0 1 0

1 1 0 0 0 0 1 1 0 1 1 1 0

1 1 0 0 0 0 0 1 0 i3 i2 i1 i0

1 1 0 0 0 0 1 1 0 1 0 1 1

1 1 0 0 0 0 1 1 0 1 1 1 1

1 1 0 0 0 0 0 1 1 i3 i2 i1 i0

1 0 0 1 0 i1 i0 a5 a4 a3 a2 a1 a0

1 0 0 1 1 i1 i0 a5 a4 a3 a2 a1 a0

1 1 0 1 1 1 1 1 1 0 0 0 X

1 1 0 1 1 1 1 1 1 0 0 1 X

1 1 0 1 1 1 1 0 0 i3 i2 i1 i0

1 1 0 1 1 1 1 1 0 0 0 0 0

1 1 0 1 1 1 1 1 0 0 0 0 1

1 1 0 1 1 1 1 1 0 0 0 1 0

1 1 0 1 1 1 1 1 0 0 0 1 1

1 1 0 1 1 1 1 1 1 0 1 0 X

1 1 0 1 1 1 1 1 1 0 1 1 X

1 1 0 1 1 1 1 0 1 i3 i2 i1 i0

1 1 0 1 1 1 1 1 0 0 1 0 0

1 1 0 1 1 1 1 1 0 0 1 0 1

1 1 0 1 1 1 1 1 0 0 1 1 0

1 1 0 1 1 1 1 1 0 0 1 1 1

1 0 0 0 0 1 0 1 0 i3 i2 i1 i0

1 1 0 1 1 1 1 1 0 1 0 0 0

1 1 0 1 1 1 1 1 0 1 1 0 0

1 1 0 1 1 1 0 0 0 i3 i2 i1 i0

1 1 0 1 1 1 1 1 0 1 0 0 1

1 1 0 1 1 1 1 1 0 1 1 0 1

1 1 0 1 1 1 0 0 1 i3 i2 i1 i0

1 1 0 1 1 1 1 1 0 1 0 1 0

1 1 0 1 1 1 1 1 0 1 1 1 0

1 1 0 1 1 1 0 1 0 i3 i2 i1 i0

1 1 0 1 1 1 1 1 0 1 0 1 1

1 1 0 1 1 1 1 1 0 1 1 1 1

1 1 0 1 1 1 0 1 1 i3 i2 i1 i0

2

↓

–

●

2

↓

–

Ч

2

↓

–

●

2

↓

–

Ч

2

↓

– – –

Ч

1

↓

–

Ч

1

↓

–

Ч

2

↓

–

●

2

↓

–

Ч

2

↓

–

●

2

↓

–

Ч

1

↓

–

↓ ↑

Ч

1

↓

–

Ч

1

↓

–

Ч

1

↓

–

●

1

↓

–

Ч

1

↓

–

●

1

↓

–

Ч

1

↓

–

Ч

1

↓

–

↓ ↑

Ч

1

↓

–

Ч

1

↓

–

●

1

↓

–

Ч

1

↓

–

●

1

↓

–

Ч

2

↓

–

●

2

↓

–

●

2

↓

–

●

2

↓

–

Ч

2

↓

–

Ч

2

↓

–

Ч

2

↓

–

●

2

↓

–

●

2

↓

–

●

2

↓

–

Ч

2

↓

–

Ч

2

↓

–

Ч

1

↓

– –

Ч

1

↓

– –

Ч

1

↓

– –

↑

Ч

1

↓

– –

Ч

1

↓

– –

Ч

1

↓

– –

●

1

↓

– –

Ч

1

↓

– –

●

1

↓

– –

Ч

1

↓

– –

Ч

1

↓

– –

↑

Ч

1

↓

– –

Ч

1

↓

– –

●

1

↓

– –

Ч

1

↓

– –

●

1

↓

– –

Ч

1

Ч

2

↓

– –

●

2

↓

– –

●

2

↓

– –

●

2

↓

– –

Ч

2

↓

– –

Ч

2

↓

– –

Ч

2

↓

– –

●

2

↓

– –

●

2

↓

– –

●

2

↓

– –

Ч

2

↓

– –

Ч

2

↓

– –

Ч

[X] (C

←

D3

←

D2

←

D1

←

D0

←

0)

[X] (C

←

D3

←

D2

←

D1

←

D0

←

0), X

←

X+1

[Y] (C

←

D3

←

D2

←

D1

←

D0

←

0)

[Y] (C

←

D3

←

D2

←

D1

←

D0

←

0), Y

←

Y+1

Sleep

A (0

→

D3

→

D2

→

D1

→

D0

→

C)

B (0

→

D3

→

D2

→

D1

→

D0

→

C)

[X] (0

→

D3

→

D2

→

D1

→

D0

→

C)

[X] (0

→

D3

→

D2

→

D1

→

D0

→

C), X

←

X+1

[Y] (0

→

D3

→

D2

→

D1

→

D0

→

C)

[Y] (0

→

D3

→

D2

→

D1

→

D0

→

C), Y

←

Y+1

A

←

A-A

A

←

A-B

A

←

A-imm4

A

←

A-[X]

A

←

A-[X], X

←

X+1

A

←

A-[Y]

A

←

A-[Y], Y

←

Y+1

B

←

B-A

B

←

B-B

B

←

B-imm4

B

←

B-[X]

B

←

B-[X], X

←

X+1

B

←

B-[Y]

B

←

B-[Y], Y

←

Y+1

[X]

←

[X]-A

[X]

←

[X]-B

[X]

←

[X]-imm4

[X]

←

[X]-A, X

←

X+1

[X]

←

[X]-B, X

←

X+1

[X]

←

[X]-imm4, X

←

X+1

[Y]

←

[Y]-A

[Y]

←

[Y]-B

[Y]

←

[Y]-imm4

[Y]

←

[Y]-A, Y

←

Y+1

[Y]

←

[Y]-B, Y

←

Y+1

[Y]

←

[Y]-imm4, Y

←

Y+1

[00addr6]

∧

(2

imm2

)

[FFaddr6]

∧

(2

imm2

)

A

←

A

∀

A

A

←

A

∀

B

A

←

A

∀

imm4

A

←

A

∀

[X]

A

←

A

∀

[X], X

←

X+1

A

←

A

∀

[Y]

A

←

A

∀

[Y], Y

←

Y+1

B

←

B

∀

A

B

←

B

∀

B

B

←

B

∀

imm4

B

←

B

∀

[X]

B

←

B

∀

[X], X

←

X+1

B

←

B

∀

[Y]

B

←

B

∀

[Y], Y

←

Y+1

F

←

F

∀

imm4

[X]

←

[X]

∀

A

[X]

←

[X]

∀

B

[X]

←

[X]

∀

imm4

[X]

←

[X]

∀

A, X

←

X+1

[X]

←

[X]

∀

B, X

←

X+1

[X]

←

[X]

∀

imm4, X

←

X+1

[Y]

←

[Y]

∀

A

[Y]

←

[Y]

∀

B

[Y]

←

[Y]

∀

imm4

[Y]

←

[Y]

∀

A, Y

←

Y+1

[Y]

←

[Y]

∀

B, Y

←

Y+1

[Y]

←

[Y]

∀

imm4, Y

←

Y+1

Mnemonic

Machine code

Operation

Cycle

Page

Flag

EXT.

mode

12

E I C Z

11 10 9 8 7 6 5 4 3 2 1 0

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔ ↔ ↔ ↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

132

132

132

132

133

133

133

134

134

134

134

135

135

135

136

136

136

136

135

135

135

136

136

136

136

137

137

138

137

137

138

137

137

138

137

137

138

139

139

139

139

140

141

141

141

141

139

139

140

141

141

141

141

140

142

142

143

142

142

143

142

142

143

142

142

143