Bit absolute addressing (4/4) – Epson S1C63000 User Manual

Page 64

58

EPSON

S1C63000 CORE CPU MANUAL

CHAPTER 4: INSTRUCTION SET

↓

– –

↓

– –

↓

– –

↓

– –

↓

– –

↓

– –

↓

– –

↓

– –

↓

– –

↓

– –

↓

– –

↓

– –

↓

– –

↓

– –

↓

– –

↓

– –

↓

– –

↓

– –

↓

– –

↓

– –

↓

– –

↓

– –

↓

– –

↓

–

↓

–

↓

–

↓

–

↓

–

↓

–

↓

–

↓

–

[FFimm8]

←

[FFimm8]

∨

A (FFimm8 = FF00H + 00H ~ FFH)

[FFimm8]

←

[FFimm8]

∨

B

[FFimm8]

←

[FFimm8]

∨

imm4

A

←

A

∀

[00imm8] (00imm8 = 0000H ~ 00FFH)

A

←

A

∀

[FFimm8]

B

←

B

∀

[00imm8]

B

←

B

∀

[FFimm8]

[00imm8]

←

[00imm8]

∀

A

[00imm8]

←

[00imm8]

∀

B

[00imm8]

←

[00imm8]

∀

imm4

[FFimm8]

←

[FFimm8]

∀

A

[FFimm8]

←

[FFimm8]

∀

B

[FFimm8]

←

[FFimm8]

∀

imm4

A

∧

[00imm8]

A

∧

[FFimm8]

B

∧

[00imm8]

B

∧

[FFimm8]

[00imm8]

∧

A

[00imm8]

∧

B

[00imm8]

∧

imm4

[FFimm8]

∧

A

[FFimm8]

∧

B

[FFimm8]

∧

imm4

[00imm8] (C

←

D3

←

D2

←

D1

←

D0

←

0)

[FFimm8] (C

←

D3

←

D2

←

D1

←

D0

←

0)

[00imm8] (0

→

D3

→

D2

→

D1

→

D0

→

C)

[FFimm8] (0

→

D3

→

D2

→

D1

→

D0

→

C)

[00imm8] (C

←

D3

←

D2

←

D1

←

D0

←

C)

[FFimm8] (C

←

D3

←

D2

←

D1

←

D0

←

C)

[00imm8] (C

→

D3

→

D2

→

D1

→

D0

→

C)

[FFimm8] (C

→

D3

→

D2

→

D1

→

D0

→

C)

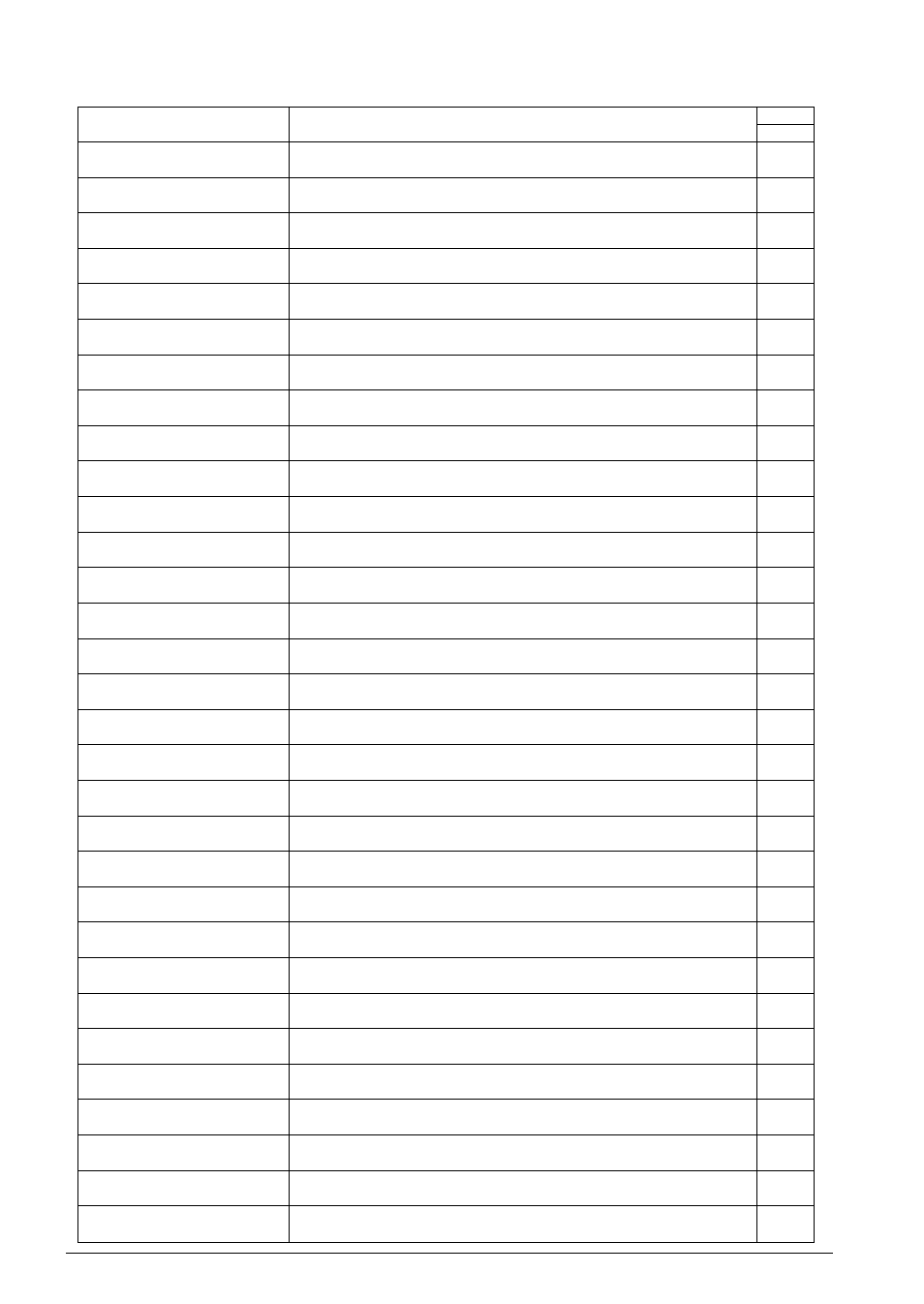

Mnemonic

Operation

Flag

E I C Z

8-bit absolute addressing (4/4)

LDB

%EXT,imm8

OR

[%Y],%A

LDB

%EXT,imm8

OR

[%Y],%B

LDB

%EXT,imm8

OR

[%Y],imm4

LDB

%EXT,imm8

XOR

%A,[%X]

LDB

%EXT,imm8

XOR

%A,[%Y]

LDB

%EXT,imm8

XOR

%B,[%X]

LDB

%EXT,imm8

XOR

%B,[%Y]

LDB

%EXT,imm8

XOR

[%X],%A

LDB

%EXT,imm8

XOR

[%X],%B

LDB

%EXT,imm8

XOR

[%X],imm4

LDB

%EXT,imm8

XOR

[%Y],%A

LDB

%EXT,imm8

XOR

[%Y],%B

LDB

%EXT,imm8

XOR

[%Y],imm4

LDB

%EXT,imm8

BIT

%A,[%X]

LDB

%EXT,imm8

BIT

%A,[%Y]

LDB

%EXT,imm8

BIT

%B,[%X]

LDB

%EXT,imm8

BIT

%B,[%Y]

LDB

%EXT,imm8

BIT

[%X],%A

LDB

%EXT,imm8

BIT

[%X],%B

LDB

%EXT,imm8

BIT

[%X],imm4

LDB

%EXT,imm8

BIT

[%Y],%A

LDB

%EXT,imm8

BIT

[%Y],%B

LDB

%EXT,imm8

BIT

[%Y],imm4

LDB

%EXT,imm8

SLL

[%X]

LDB

%EXT,imm8

SLL

[%Y]

LDB

%EXT,imm8

SRL

[%X]

LDB

%EXT,imm8

SRL

[%Y]

LDB

%EXT,imm8

RL

[%X]

LDB

%EXT,imm8

RL

[%Y]

LDB

%EXT,imm8

RR

[%X]

LDB

%EXT,imm8

RR

[%Y]

↔↔↔↔↔↔↔↔↔↔↔↔↔↔↔↔↔

↔

↔

↔

↔

↔

↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔