Tst [addr6],imm2 xor %r,%r – Epson S1C63000 User Manual

Page 145

S1C63000 CORE CPU MANUAL

EPSON

139

CHAPTER 4: INSTRUCTION SET

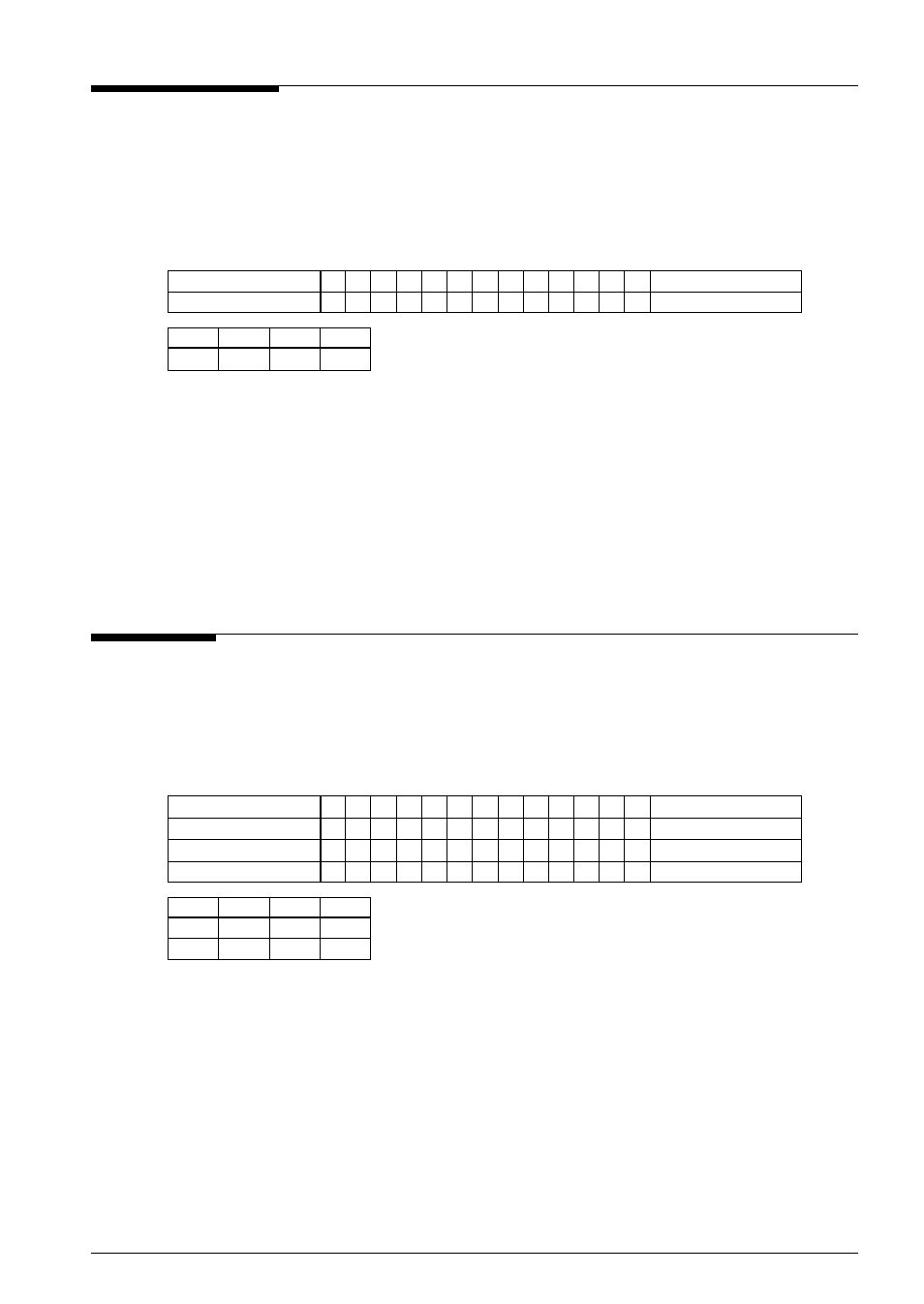

TST [addr6],imm2

XOR %r,%r’

Exclusive OR r’ reg. and r reg.

1 cycle

Function:

r

←

r

∀

r’

Performs an exclusive OR operation of the content of the r’ register (A or B) and the content of

the r register (A or B), and stores the result in the r register.

Code:

Mnemonic

MSB

LSB

XOR %A,%A

1

1

0

1

1

1

1

1

1

0

0

0

X

1BF0H, (1BF1H)

XOR %A,%B

1

1

0

1

1

1

1

1

1

0

0

1

X

1BF2H, (1BF3H)

XOR %B,%A

1

1

0

1

1

1

1

1

1

0

1

0

X

1BF4H, (1BF5H)

XOR %B,%B

1

1

0

1

1

1

1

1

1

0

1

1

X

1BF6H, (1BF7H)

Flags:

E

I

C

Z

↓

–

–

↕

(r

≠

r’)

↓

–

–

↑

(r = r’)

Mode:

Src: Register direct

Dst: Register direct

Extended addressing: Invalid

Test bit imm2 in location [addr6]

1 cycle

Function:

[addr6]

∨

(2

imm2

)

(addr6 = 0000H–003FH or FFC0H–FFFFH)

Tests the bit specified with the imm2 in the data memory specified with the addr6, and sets/

resets the Z flag. It does not change the content of the data memory.

Code:

Mnemonic

MSB

LSB

TST [00addr6],imm2 1

0

0

1

0 i1 i0 a5 a4 a3 a2 a1 a0 1200H–12FFH

TST [FFaddr6],imm2 1

0

0

1

1 i1 i0 a5 a4 a3 a2 a1 a0 1300H–13FFH

Flags:

E

I

C

Z

↓

–

–

↕

Mode:

Src: Immediate data

Dst: 6-bit absolute

Extended addressing: Invalid