2 initial setting of internal registers, 5 interrupts, 1 interrupt vectors – Epson S1C63000 User Manual

Page 32

26

EPSON

S1C63000 CORE CPU MANUAL

CHAPTER 3: CPU OPERATION

After an initial reset, all the interrupts including NMI are masked until both the stack pointers SP1 and

SP2 are set by software.

3.4.2 Initial setting of internal registers

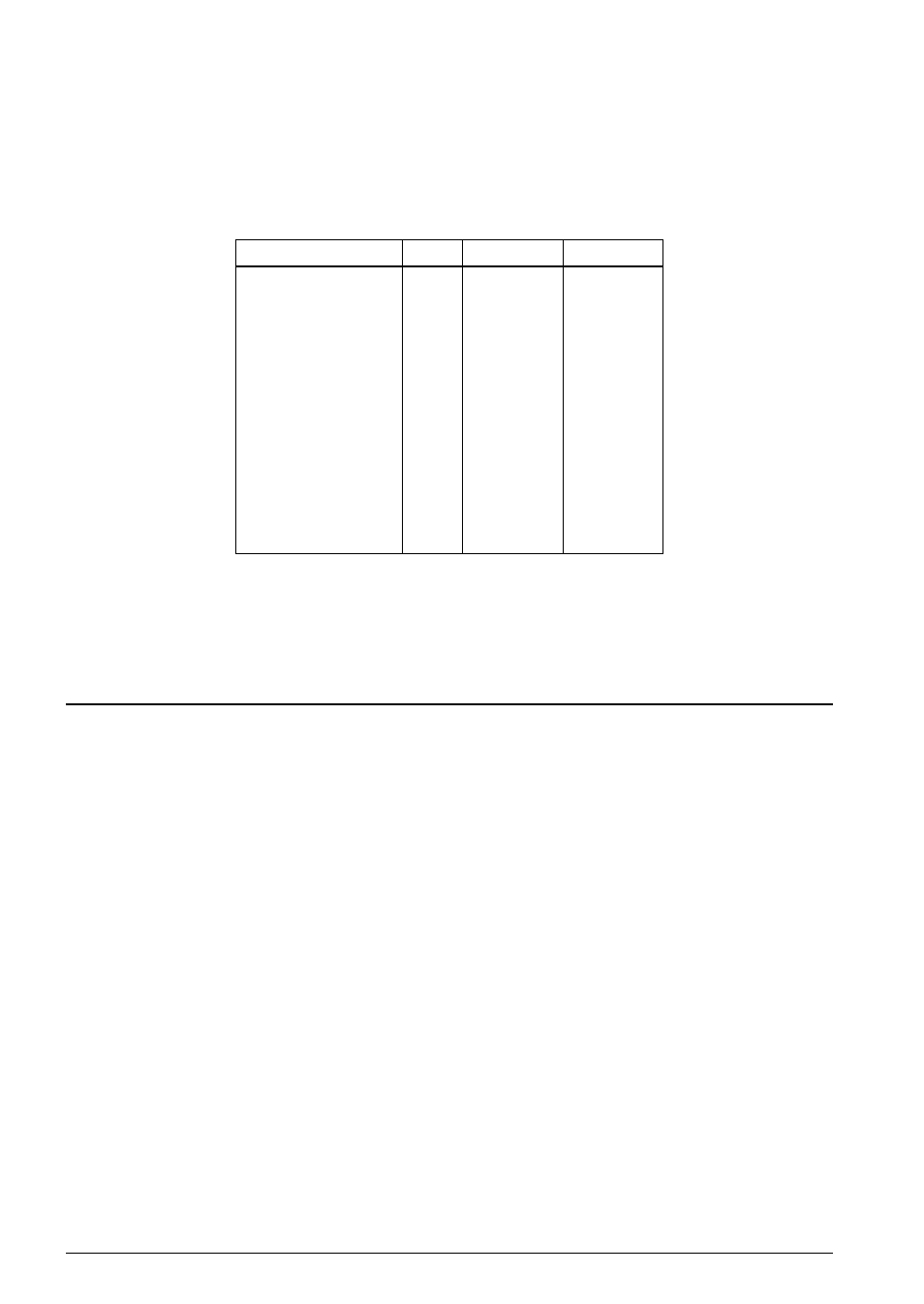

An initial reset initializes the internal registers in the CPU as shown in Table 3.4.2.1.

Table 3.4.2.1 Initial setting of internal registers

Name

Data register A

Data register B

Extension register EXT

Index register X

Index register Y

Program counter

Stack pointer SP1

Stack pointer SP2

Zero flag

Carry flag

Interrupt flag

Extension flag

Queue register

Setting value

Undefined

Undefined

Undefined

Undefined

Undefined

0110H

Undefined

Undefined

Undefined

Undefined

0

0

Undefined

Number of bits

4

4

8

16

16

16

8

8

1

1

1

1

16

Symbol

A

B

EXT

X

Y

PC

SP1

SP2

Z

C

I

E

Q

The registers and flags which are not initialized at an initial reset should be initialized in the program if

necessary.

Be sure to set both the stack pointers SP1 and SP2. All the interrupts cannot be accepted if they are not set

as a pair.

3.5 Interrupts

Interrupt is a function to process factors, that generate asynchronously with program execution, such as a

key entry and an end of a peripheral circuit operation. When the CPU accepts an interrupt request that is

sent by the hardware, the CPU stops executing the current sequence of the program and shifts into the

interrupt processing. When all the interrupt processing has finished, the interrupted program is resumed.

The S1C63000 has the hardware interrupt function for the peripheral circuits including an NMI (non-

maskable interrupt) and the hardware interrupt function. The hardware interrupts excluding the NMI

can be set to the DI (disable interrupts) status by setting the I (interrupt) flag.

I flag = "1": EI (enable interrupts) status

...The CPU accepts interrupt requests from the peripheral

circuits.

I flag = "0": DI (disable interrupts) status

...The CPU does not accept interrupt requests from the periph-

eral circuits. (excluding NMI and software interrupts)

The I flag is set to "0" at an initial reset. Furthermore, all the interrupts including NMI are masked and

cannot be accepted regardless of the I flag setting until both the stack pointers SP1 and SP2 are set in the

program after an initial reset.

3.5.1 Interrupt vectors

Interrupt vectors are provided to execute a interrupt service routine corresponding to the interrupt

generated.

The interrupt vectors are assigned to the following addresses in the ROM.

NMI interrupt vector:

0100H

Hardware interrupt vectors:

0101H to 010FH

Software interrupt vectors:

0111H to 013FH