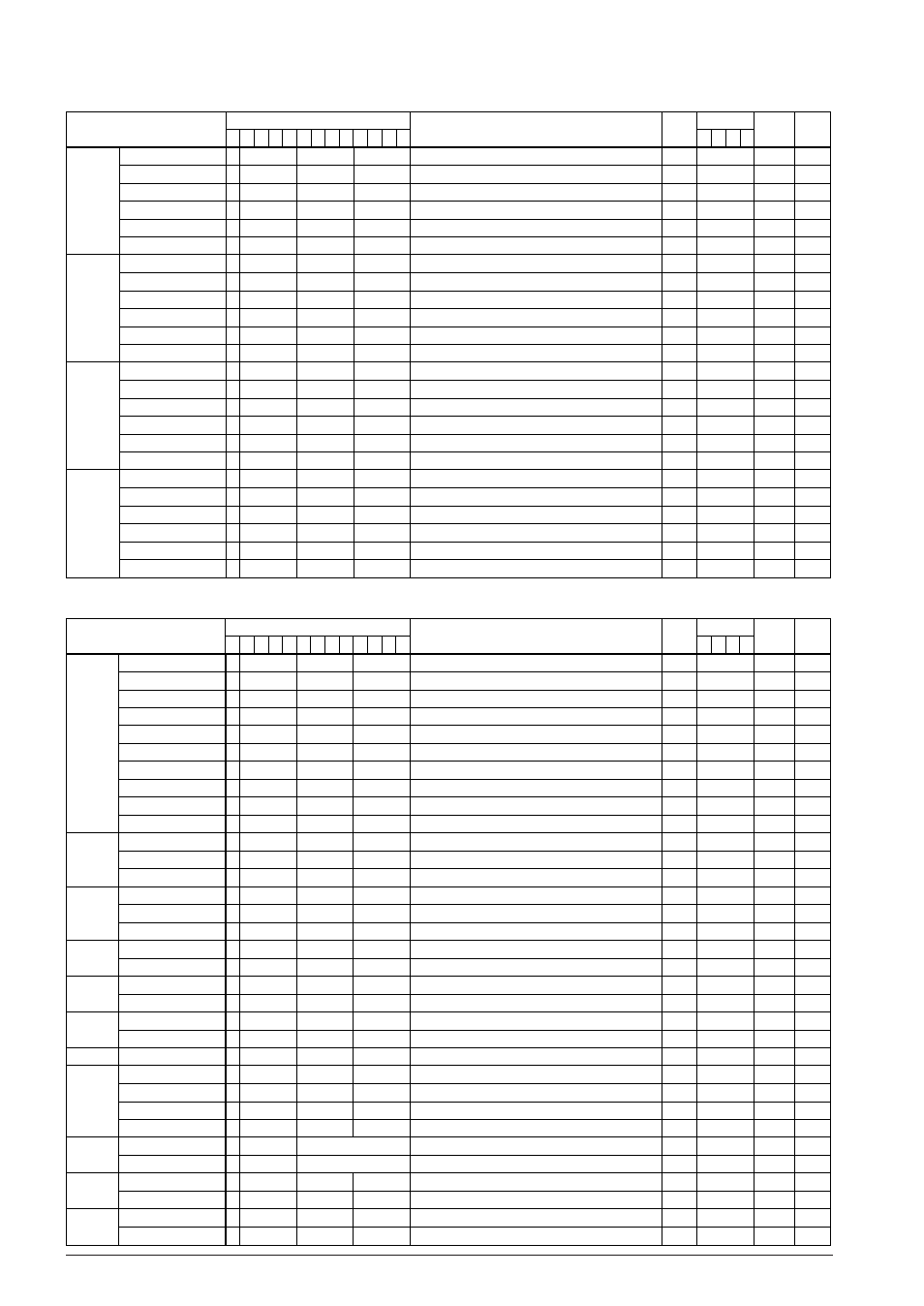

Alu shift and rotate operation, 8/16-bit operation – Epson S1C63000 User Manual

Page 52

46

EPSON

S1C63000 CORE CPU MANUAL

CHAPTER 4: INSTRUCTION SET

SLL

%A

%B

[%X]

[%X]+

[%Y]

[%Y]+

SRL

%A

%B

[%X]

[%X]+

[%Y]

[%Y]+

RL

%A

%B

[%X]

[%X]+

[%Y]

[%Y]+

RR

%A

%B

[%X]

[%X]+

[%Y]

[%Y]+

1 0 0 0 0 1 1 1 1 0 0 0 0

1 0 0 0 0 1 1 1 1 0 1 0 0

1 0 0 0 0 1 1 1 0 0 0 0 0

1 0 0 0 0 1 1 1 0 0 0 0 1

1 0 0 0 0 1 1 1 0 0 0 1 0

1 0 0 0 0 1 1 1 0 0 0 1 1

1 0 0 0 0 1 1 1 1 0 0 0 1

1 0 0 0 0 1 1 1 1 0 1 0 1

1 0 0 0 0 1 1 1 0 0 1 0 0

1 0 0 0 0 1 1 1 0 0 1 0 1

1 0 0 0 0 1 1 1 0 0 1 1 0

1 0 0 0 0 1 1 1 0 0 1 1 1

1 0 0 0 0 1 1 1 1 0 0 1 0

1 0 0 0 0 1 1 1 1 0 1 1 0

1 0 0 0 0 1 1 1 0 1 0 0 0

1 0 0 0 0 1 1 1 0 1 0 0 1

1 0 0 0 0 1 1 1 0 1 0 1 0

1 0 0 0 0 1 1 1 0 1 0 1 1

1 0 0 0 0 1 1 1 1 0 0 1 1

1 0 0 0 0 1 1 1 1 0 1 1 1

1 0 0 0 0 1 1 1 0 1 1 0 0

1 0 0 0 0 1 1 1 0 1 1 0 1

1 0 0 0 0 1 1 1 0 1 1 1 0

1 0 0 0 0 1 1 1 0 1 1 1 1

1

↓

–

Ч

1

↓

–

Ч

2

↓

–

●

2

↓

–

Ч

2

↓

–

●

2

↓

–

Ч

1

↓

–

Ч

1

↓

–

Ч

2

↓

–

●

2

↓

–

Ч

2

↓

–

●

2

↓

–

Ч

1

↓

–

Ч

1

↓

–

Ч

2

↓

–

●

2

↓

–

Ч

2

↓

–

●

2

↓

–

Ч

1

↓

–

Ч

1

↓

–

Ч

2

↓

–

●

2

↓

–

Ч

2

↓

–

●

2

↓

–

Ч

A (C

←

D3

←

D2

←

D1

←

D0

←

0)

B (C

←

D3

←

D2

←

D1

←

D0

←

0)

[X] (C

←

D3

←

D2

←

D1

←

D0

←

0)

[X] (C

←

D3

←

D2

←

D1

←

D0

←

0), X

←

X+1

[Y] (C

←

D3

←

D2

←

D1

←

D0

←

0)

[Y] (C

←

D3

←

D2

←

D1

←

D0

←

0), Y

←

Y+1

A (0

→

D3

→

D2

→

D1

→

D0

→

C)

B (0

→

D3

→

D2

→

D1

→

D0

→

C)

[X] (0

→

D3

→

D2

→

D1

→

D0

→

C)

[X] (0

→

D3

→

D2

→

D1

→

D0

→

C), X

←

X+1

[Y] (0

→

D3

→

D2

→

D1

→

D0

→

C)

[Y] (0

→

D3

→

D2

→

D1

→

D0

→

C), Y

←

Y+1

A (C

←

D3

←

D2

←

D1

←

D0

←

C)

B (C

←

D3

←

D2

←

D1

←

D0

←

C)

[X] (C

←

D3

←

D2

←

D1

←

D0

←

C)

[X] (C

←

D3

←

D2

←

D1

←

D0

←

C), X

←

X+1

[Y] (C

←

D3

←

D2

←

D1

←

D0

←

C)

[Y] (C

←

D3

←

D2

←

D1

←

D0

←

C), Y

←

Y+1

A (C

→

D3

→

D2

→

D1

→

D0

→

C)

B (C

→

D3

→

D2

→

D1

→

D0

→

C)

[X] (C

→

D3

→

D2

→

D1

→

D0

→

C)

[X] (C

→

D3

→

D2

→

D1

→

D0

→

C), X

←

X+1

[Y] (C

→

D3

→

D2

→

D1

→

D0

→

C)

[Y] (C

→

D3

→

D2

→

D1

→

D0

→

C), Y

←

Y+1

Mnemonic

Machine code

Operation

Cycle

Page

Flag

EXT.

mode

12

E I C Z

11 10 9 8 7 6 5 4 3 2 1 0

↔ ↔

ALU shift and rotate operation

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

↔ ↔

131

131

132

132

132

132

133

133

134

134

134

134

120

120

121

121

121

121

122

122

122

123

122

123

LDB

%BA,%XL

%BA,%XH

%BA,%YL

%BA,%YH

%BA,%EXT

%BA,%SP1

%BA,%SP2

%BA,imm8

%BA,[%X]+

%BA,[%Y]+

LDB

%XL,%BA

%XL,imm8

%XH,%BA

LDB

%YL,%BA

%YL,imm8

%YH,%BA

LDB

%EXT,%BA

%EXT,imm8

LDB

%SP1,%BA

%SP2,%BA

LDB

[%X]+,%BA

[%X]+,imm8

LDB

[%Y]+,%BA

ADD

%X,%BA

%X,sign8

%Y,%BA

%Y,sign8

CMP

%X,imm8

%Y,imm8

INC

%SP1

%SP2

DEC

%SP1

%SP2

1 1 1 1 1 1 1 0 0 1 0 0 0

1 1 1 1 1 1 1 0 0 1 0 0 1

1 1 1 1 1 1 1 0 0 1 0 1 0

1 1 1 1 1 1 1 0 0 1 0 1 1

1 1 1 1 1 1 1 0 1 0 1 1 X

1 1 1 1 1 1 1 0 0 1 1 0 X

1 1 1 1 1 1 1 0 0 1 1 1 X

0 1 0 0 1 i7 i6 i5 i4 i3 i2 i1 i0

1 1 1 1 1 1 1 0 1 1 0 0 0

1 1 1 1 1 1 1 0 1 1 0 1 0

1 1 1 1 1 1 1 0 0 0 0 0 0

0 1 0 1 0 i7 i6 i5 i4 i3 i2 i1 i0

1 1 1 1 1 1 1 0 0 0 0 0 1

1 1 1 1 1 1 1 0 0 0 0 1 0

0 1 0 1 1 i7 i6 i5 i4 i3 i2 i1 i0

1 1 1 1 1 1 1 0 0 0 0 1 1

1 1 1 1 1 1 1 0 1 0 1 0 X

0 1 0 0 0 i7 i6 i5 i4 i3 i2 i1 i0

1 1 1 1 1 1 1 0 0 0 1 0 X

1 1 1 1 1 1 1 0 0 0 1 1 X

1 1 1 1 1 1 1 0 1 1 0 0 1

0 0 0 0 1 i7 i6 i5 i4 i3 i2 i1 i0

1 1 1 1 1 1 1 0 1 1 0 1 1

1 1 1 1 1 1 1 0 1 0 0 0 X

0 1 1 0 0 s7 s6 s5 s4 s3 s2 s1 s0

1 1 1 1 1 1 1 0 1 0 0 1 X

0 1 1 0 1 s7 s6 s5 s4 s3 s2 s1 s0

0 1 1 1 0 [

FFH - imm8

]

0 1 1 1 1 [

FFH - imm8

]

1 1 1 1 1 1 1 1 0 1 0 0 0

1 1 1 1 1 1 1 1 0 1 1 0 0

1 1 1 1 1 1 1 1 0 0 0 0 0

1 1 1 1 1 1 1 1 0 0 1 0 0

1

↓

– – –

Ч

1

↓

– – –

Ч

1

↓

– – –

Ч

1

↓

– – –

Ч

1

↓

– – –

Ч

1

↓

– – –

Ч

1

↓

– – –

Ч

1

↓

– – –

Ч

2

↓

– – –

Ч

2

↓

– – –

Ч

1

↓

– – –

Ч

1

↓

– – –

●

1

↓

– – –

Ч

1

↓

– – –

Ч

1

↓

– – –

●

1

↓

– – –

Ч

1

↑

– – –

Ч

1

↑

– – –

Ч

1

↓

– – –

Ч

1

↓

– – –

Ч

2

↓

– – –

Ч

2

↓

– – –

Ч

2

↓

– – –

Ч

1

↓

– –

Ч

1

↓

– –

●

1

↓

– –

Ч

1

↓

– –

●

1

↓

–

●

1

↓

–

●

1

↓

– –

Ч

1

↓

– –

Ч

1

↓

– –

Ч

1

↓

– –

Ч

BA

←

XL

BA

←

XH

BA

←

YL

BA

←

YH

BA

←

EXT

BA

←

SP1

BA

←

SP2

BA

←

imm8

A

←

[X], B

←

[X+1], X

←

X+2

A

←

[Y], B

←

[Y+1], Y

←

Y+2

XL

←

BA

XL

←

imm8

XH

←

BA

YL

←

BA

YL

←

imm8

YH

←

BA

EXT

←

BA

EXT

←

imm8

SP1

←

BA

SP2

←

BA

[X]

←

A, [X+1]

←

B, X

←

X+2

[X]

←

i3~0, [X+1]

←

i7~4, X

←

X+2

[Y]

←

A, [Y+1]

←

B, Y

←

Y+2

X

←

X+BA

X

←

X+sign8 (sign8=-128~127)

Y

←

Y+BA

Y

←

Y+sign8 (sign8=-128~127)

X-imm8 (imm8=0~255)

Y-imm8 (imm8=0~255)

SP1

←

SP1+1

SP2

←

SP2+1

SP1

←

SP1-1

SP2

←

SP2-1

Mnemonic

Machine code

Operation

Cycle

Page

Flag

EXT.

mode

12

E I C Z

11 10 9 8 7 6 5 4 3 2 1 0

8/16-bit operation

↔ ↔

↔ ↔

↔

↔

↔↔

↔

↔

↔

↔

107

107

107

107

106

107

107

105

106

106

110

110

110

110

110

110

109

109

111

111

108

108

108

72

72

72

72

88

88

94

94

90

90