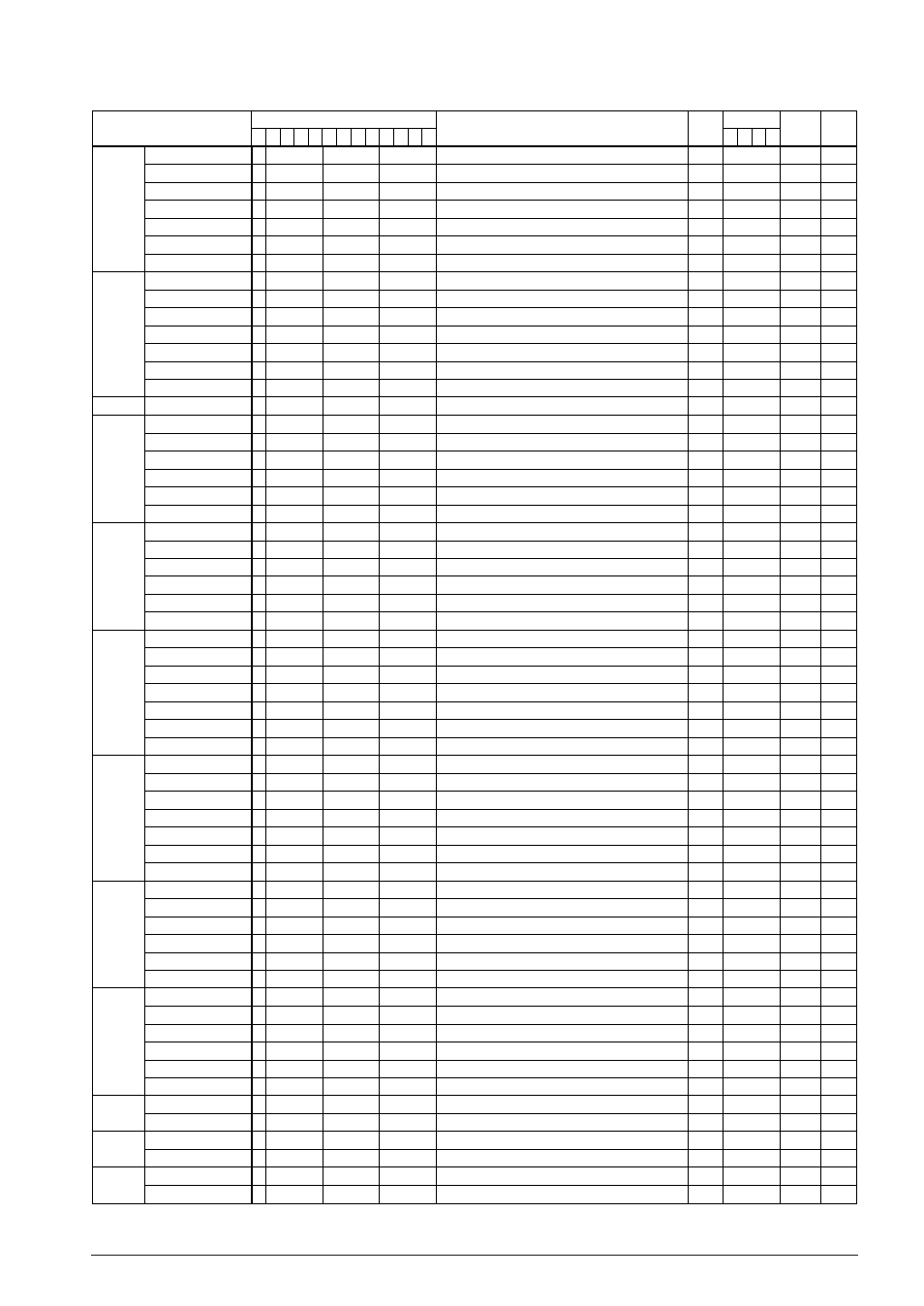

Alu logic operation (2/2) – Epson S1C63000 User Manual

Page 51

S1C63000 CORE CPU MANUAL

EPSON

45

CHAPTER 4: INSTRUCTION SET

XOR

%A,%A

%A,%B

%A,imm4

%A,[%X]

%A,[%X]+

%A,[%Y]

%A,[%Y]+

XOR

%B,%A

%B,%B

%B,imm4

%B,[%X]

%B,[%X]+

%B,[%Y]

%B,[%Y]+

XOR

%F,imm4

XOR

[%X],%A

[%X],%B

[%X],imm4

[%X]+,%A

[%X]+,%B

[%X]+,imm4

XOR

[%Y],%A

[%Y],%B

[%Y],imm4

[%Y]+,%A

[%Y]+,%B

[%Y]+,imm4

BIT

%A,%A

%A,%B

%A,imm4

%A,[%X]

%A,[%X]+

%A,[%Y]

%A,[%Y]+

BIT

%B,%A

%B,%B

%B,imm4

%B,[%X]

%B,[%X]+

%B,[%Y]

%B,[%Y]+

BIT

[%X],%A

[%X],%B

[%X],imm4

[%X]+,%A

[%X]+,%B

[%X]+,imm4

BIT

[%Y],%A

[%Y],%B

[%Y],imm4

[%Y]+,%A

[%Y]+,%B

[%Y]+,imm4

CLR

[00addr6],imm2

[FFaddr6],imm2

SET

[00addr6],imm2

[FFaddr6],imm2

TST

[00addr6],imm2

[FFaddr6],imm2

1 1 0 1 1 1 1 1 1 0 0 0 X

1 1 0 1 1 1 1 1 1 0 0 1 X

1 1 0 1 1 1 1 0 0 i3 i2 i1 i0

1 1 0 1 1 1 1 1 0 0 0 0 0

1 1 0 1 1 1 1 1 0 0 0 0 1

1 1 0 1 1 1 1 1 0 0 0 1 0

1 1 0 1 1 1 1 1 0 0 0 1 1

1 1 0 1 1 1 1 1 1 0 1 0 X

1 1 0 1 1 1 1 1 1 0 1 1 X

1 1 0 1 1 1 1 0 1 i3 i2 i1 i0

1 1 0 1 1 1 1 1 0 0 1 0 0

1 1 0 1 1 1 1 1 0 0 1 0 1

1 1 0 1 1 1 1 1 0 0 1 1 0

1 1 0 1 1 1 1 1 0 0 1 1 1

1 0 0 0 0 1 0 1 0 i3 i2 i1 i0

1 1 0 1 1 1 1 1 0 1 0 0 0

1 1 0 1 1 1 1 1 0 1 1 0 0

1 1 0 1 1 1 0 0 0 i3 i2 i1 i0

1 1 0 1 1 1 1 1 0 1 0 0 1

1 1 0 1 1 1 1 1 0 1 1 0 1

1 1 0 1 1 1 0 0 1 i3 i2 i1 i0

1 1 0 1 1 1 1 1 0 1 0 1 0

1 1 0 1 1 1 1 1 0 1 1 1 0

1 1 0 1 1 1 0 1 0 i3 i2 i1 i0

1 1 0 1 1 1 1 1 0 1 0 1 1

1 1 0 1 1 1 1 1 0 1 1 1 1

1 1 0 1 1 1 0 1 1 i3 i2 i1 i0

1 1 0 1 0 1 1 1 1 0 0 0 X

1 1 0 1 0 1 1 1 1 0 0 1 X

1 1 0 1 0 1 1 0 0 i3 i2 i1 i0

1 1 0 1 0 1 1 1 0 0 0 0 0

1 1 0 1 0 1 1 1 0 0 0 0 1

1 1 0 1 0 1 1 1 0 0 0 1 0

1 1 0 1 0 1 1 1 0 0 0 1 1

1 1 0 1 0 1 1 1 1 0 1 0 X

1 1 0 1 0 1 1 1 1 0 1 1 X

1 1 0 1 0 1 1 0 1 i3 i2 i1 i0

1 1 0 1 0 1 1 1 0 0 1 0 0

1 1 0 1 0 1 1 1 0 0 1 0 1

1 1 0 1 0 1 1 1 0 0 1 1 0

1 1 0 1 0 1 1 1 0 0 1 1 1

1 1 0 1 0 1 1 1 0 1 0 0 0

1 1 0 1 0 1 1 1 0 1 1 0 0

1 1 0 1 0 1 0 0 0 i3 i2 i1 i0

1 1 0 1 0 1 1 1 0 1 0 0 1

1 1 0 1 0 1 1 1 0 1 1 0 1

1 1 0 1 0 1 0 0 1 i3 i2 i1 i0

1 1 0 1 0 1 1 1 0 1 0 1 0

1 1 0 1 0 1 1 1 0 1 1 1 0

1 1 0 1 0 1 0 1 0 i3 i2 i1 i0

1 1 0 1 0 1 1 1 0 1 0 1 1

1 1 0 1 0 1 1 1 0 1 1 1 1

1 1 0 1 0 1 0 1 1 i3 i2 i1 i0

1 0 1 0 0 i1 i0 a5 a4 a3 a2 a1 a0

1 0 1 0 1 i1 i0 a5 a4 a3 a2 a1 a0

1 0 1 1 0 i1 i0 a5 a4 a3 a2 a1 a0

1 0 1 1 1 i1 i0 a5 a4 a3 a2 a1 a0

1 0 0 1 0 i1 i0 a5 a4 a3 a2 a1 a0

1 0 0 1 1 i1 i0 a5 a4 a3 a2 a1 a0

1

↓

– –

↑

Ч

1

↓

– –

Ч

1

↓

– –

Ч

1

↓

– –

●

1

↓

– –

Ч

1

↓

– –

●

1

↓

– –

Ч

1

↓

– –

Ч

1

↓

– –

↑

Ч

1

↓

– –

Ч

1

↓

– –

●

1

↓

– –

Ч

1

↓

– –

●

1

↓

– –

Ч

1

Ч

2

↓

– –

●

2

↓

– –

●

2

↓

– –

●

2

↓

– –

Ч

2

↓

– –

Ч

2

↓

– –

Ч

2

↓

– –

●

2

↓

– –

●

2

↓

– –

●

2

↓

– –

Ч

2

↓

– –

Ч

2

↓

– –

Ч

1

↓

– –

Ч

1

↓

– –

Ч

1

↓

– –

Ч

1

↓

– –

●

1

↓

– –

Ч

1

↓

– –

●

1

↓

– –

Ч

1

↓

– –

Ч

1

↓

– –

Ч

1

↓

– –

Ч

1

↓

– –

●

1

↓

– –

Ч

1

↓

– –

●

1

↓

– –

Ч

1

↓

– –

●

1

↓

– –

●

1

↓

– –

●

1

↓

– –

Ч

1

↓

– –

Ч

1

↓

– –

Ч

1

↓

– –

●

1

↓

– –

●

1

↓

– –

●

1

↓

– –

Ч

1

↓

– –

Ч

1

↓

– –

Ч

2

↓

– –

Ч

2

↓

– –

Ч

2

↓

– –

Ч

2

↓

– –

Ч

1

↓

– –

Ч

1

↓

– –

Ч

A

←

A

∀

A

A

←

A

∀

B

A

←

A

∀

imm4

A

←

A

∀

[X]

A

←

A

∀

[X], X

←

X+1

A

←

A

∀

[Y]

A

←

A

∀

[Y], Y

←

Y+1

B

←

B

∀

A

B

←

B

∀

B

B

←

B

∀

imm4

B

←

B

∀

[X]

B

←

B

∀

[X], X

←

X+1

B

←

B

∀

[Y]

B

←

B

∀

[Y], Y

←

Y+1

F

←

F

∀

imm4

[X]

←

[X]

∀

A

[X]

←

[X]

∀

B

[X]

←

[X]

∀

imm4

[X]

←

[X]

∀

A, X

←

X+1

[X]

←

[X]

∀

B, X

←

X+1

[X]

←

[X]

∀

imm4, X

←

X+1

[Y]

←

[Y]

∀

A

[Y]

←

[Y]

∀

B

[Y]

←

[Y]

∀

imm4

[Y]

←

[Y]

∀

A, Y

←

Y+1

[Y]

←

[Y]

∀

B, Y

←

Y+1

[Y]

←

[Y]

∀

imm4, Y

←

Y+1

A

∧

A

A

∧

B

A

∧

imm4

A

∧

[X]

A

∧

[X], X

←

X+1

A

∧

[Y]

A

∧

[Y], Y

←

Y+1

B

∧

A

B

∧

B

B

∧

imm4

B

∧

[X]

B

∧

[X], X

←

X+1

B

∧

[Y]

B

∧

[Y], Y

←

Y+1

[X]

∧

A

[X]

∧

B

[X]

∧

imm4

[X]

∧

A, X

←

X+1

[X]

∧

B, X

←

X+1

[X]

∧

imm4, X

←

X+1

[Y]

∧

A

[Y]

∧

B

[Y]

∧

imm4

[Y]

∧

A, Y

←

Y+1

[Y]

∧

B, Y

←

Y+1

[Y]

∧

imm4, Y

←

Y+1

[00addr6]

←

[00addr6]

∧

not (2

imm2

)

[FFaddr6]

←

[FFaddr6]

∧

not (2

imm2

)

[00addr6]

←

[00addr6]

∧

(2

imm2

)

[FFaddr6]

←

[FFaddr6]

∧

(2

imm2

)

[00addr6]

∧

(2

imm2

)

[FFaddr6]

∧

(2

imm2

)

Mnemonic

Machine code

Operation

Cycle

Page

Flag

EXT.

mode

12

E I C Z

11 10 9 8 7 6 5 4 3 2 1 0

ALU logic operation (2/2)

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔ ↔ ↔ ↔

↔

↔

↔

↔

↔↔

139

139

140

141

141

141

141

139

139

140

141

141

141

141

140

142

142

143

142

142

143

142

142

143

142

142

143

78

78

78

79

79

79

79

78

78

78

79

79

79

79

80

80

81

80

80

81

80

80

81

80

80

81

83

83

131

131

139

139